## The Co-Design of Virtual Machines Using Reconfigurable Hardware

by

Kenneth Blair Kent B.Sc. (*hons*), Memorial University of Newfoundland, 1996 M.Sc., University of Victoria, 1999

A Dissertation Submitted in Partial Fulfillment of the Requirements for the Degree of

#### DOCTORATE OF PHILOSOPHY

in the Department of Computer Science

We accept this dissertation as conforming to the required standard

Dr. M. Serra, Supervisor (Department of Computer Science)

Dr. M. Cheng, Member (Department of Computer Science)

Dr. N. Horspool, Member (Department of Computer Science)

Dr. K. Li, Outside Member (Department of Electrical and Computer Engineering)

Dr. R. McLeod, External Examiner (University of Manitoba, Department of Electrical and Computer Engineering)

© Kenneth B. Kent, 2003 University of Victoria

All rights reserved. This dissertation may not be reproduced in whole or in part, by photocopying or other means, without the permission of the author.

Supervisor: Dr. M. Serra

### <u>ABSTRACT</u>

The prominence of the internet and networked computing has driven research efforts into providing support for heterogeneous computing platforms. This has been exemplified by the emergence of virtual machines, such as the Java virtual machine. Unfortunately, most virtual computing platforms come with a performance penalty. This dissertation investigates a new approach for providing virtual computing platforms through the use of reconfigurable computing devices and hardware/software co-design.

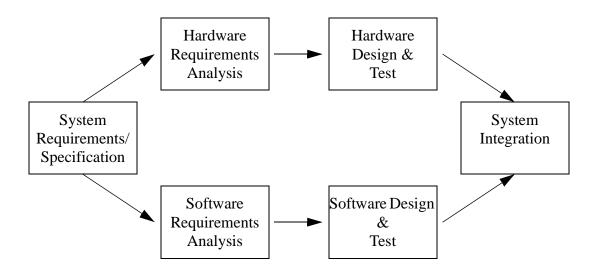

Traditionally, when designing a hardware/software solution, instance specific methods are used to iterate towards a solution that satisfies the requirements. This is not an ideal approach as the costs involved with integrating hardware and software components are significant. This technique demotes the interface between the hardware and software, often resulting in major complications at the integration stage. These problems can be avoided through adherence to a sound methodology which the co-design process follows.

This dissertation examines the original concept of using hardware/software codesign and reconfigurable computing as a means of providing virtual machine platforms. Specifically the contributions include an advancement towards a new general computing paradigm and architecture; guidelines and several algorithms for applying the general hardware/software co-design process to the specific virtual machine class of problems; and an assessment of the potential advantages of using co-design as an implementation approach for virtual machines. These are applied to the Java virtual machine and simulated for insights into the potential benefits, requirements, and caveats of co-design for virtual machines.

This research demonstrates that using hardware/software co-design as described specifically for virtual machines, the solution can offer performance benefits over a software-only solution. These performance increases will be shown to be dependent upon several factors such as the application itself and the underlying architectural features. This dissertation will promote and give evidence that reconfigurable computing can be used for more general purpose computing and not just for specific problem instances.

Dr. M. Cheng, Member (Department of Computer Science)

Dr. N. Horspool, Member (Department of Computer Science)

Dr. K. Li, Outside Member (Department of Electrical and Computer Engineering)

Dr. R. McLeod, External Examiner (University of Manitoba, Department of Electrical and Computer Engineering)

## **Table of Contents**

| Abstract                                                                | ii   |

|-------------------------------------------------------------------------|------|

| Table of Contents                                                       | iv   |

| List of Figures                                                         | ix   |

| List of Tables                                                          | xiii |

| Acknowledgments                                                         | xiv  |

| Chapter 1 Introduction                                                  | 1    |

| 1.1 Research Contributions                                              | 5    |

| 1.2 Dissertation Overview                                               | 7    |

| Chapter 2 Virtual Machines                                              | 9    |

| 2.1 Introduction                                                        | 9    |

| 2.2 Virtual Machines                                                    | 9    |

| 2.3 Virtual Machine Implementation Techniques                           | 11   |

| 2.3.1 Software Interpreter                                              |      |

| 2.3.2 Just-In-Time Technology                                           |      |

| <ul><li>2.3.3 Native Processor</li><li>2.3.4 Hybrid Processor</li></ul> |      |

| 2.4 Co-Designing Virtual Machines                                       |      |

| 2.5 Benefits of a Co-Designed Virtual Machine                           |      |

| 2.6 Java Virtual Machine                                                |      |

| 2.6.1 Benchmark Tests                                                   |      |

| 2.7 Summary                                                             | 25   |

| Chapter 3 Hardware/Software Co-Design                                   |      |

| 3.1 Introduction                                                        | 26   |

| 3.2 Hardware/Software Co-Design                                         |      |

| 3.3 Issues Involved with Co-Design                                      | 30   |

| 3.3.1 Modeling                                                                        |  |

|---------------------------------------------------------------------------------------|--|

| 3.3.2 Partitioning                                                                    |  |

| 3.3.3 Co-Synthesis                                                                    |  |

| 3.3.4 Co-Simulation                                                                   |  |

| 3.4 Reconfigurable Computing                                                          |  |

| 3.4.1 Types of Reconfigurable Computing                                               |  |

| 3.4.2 Field Programmable Gate Arrays                                                  |  |

| 3.5 Summary                                                                           |  |

| Chapter 4 Co-Design Partitioning                                                      |  |

| 4.1 Introduction                                                                      |  |

|                                                                                       |  |

| 4.2 The Process of Partitioning                                                       |  |

| 4.2.1 Partitioning Approaches                                                         |  |

| 4.2.2 Exploitations of Virtual Machine Partitioning                                   |  |

| 4.2.3 Partitioning Heuristics                                                         |  |

| 4.3 Software Partition                                                                |  |

| 4.3.1 Loading Data from the Constant Pool                                             |  |

| 4.3.2 Field Accesses of Classes and Objects                                           |  |

| 4.3.3 Method Invocation                                                               |  |

| 4.3.4 Quick Method Invocation                                                         |  |

| 4.3.5 Exceptions                                                                      |  |

| 4.3.6 Object Creation                                                                 |  |

| 4.3.7 Array Creation                                                                  |  |

| 4.3.8 Storing to a Reference Array                                                    |  |

| 4.3.9 Type Checking                                                                   |  |

| 4.3.10 Monitors                                                                       |  |

| 4.3.11 Accessing the Jump Table                                                       |  |

| 4.3.12 Wide Indexing                                                                  |  |

| 4.3.13 Long Mathematical Operations                                                   |  |

| 4.3.14 Returning from a Method                                                        |  |

| 4.3.15 Operating System Support                                                       |  |

| 4.3.16 Software and Hardware Coordination                                             |  |

| 4.4 Hardware Partition                                                                |  |

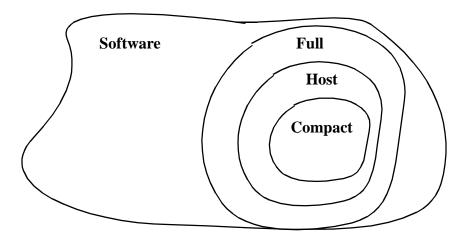

| 4.4.1 Compact Partition                                                               |  |

| 4.4.1.1 Constant Instructions<br>4.4.1.2 Stack Manipulation                           |  |

| <ul><li>4.4.1.2 Stack Manipulation</li><li>4.4.1.3 Mathematical Opcodes</li></ul>     |  |

| 4.4.1.4 Shift and Logical Opcodes                                                     |  |

| 4.4.1.5 Loading and Storing                                                           |  |

| 4.4.1.6 Casting Operators                                                             |  |

| 4.4.1.7 Comparison and Branching Operators                                            |  |

| <ul><li>4.4.1.8 Jump and Return</li><li>4.4.1.9 Miscellaneous Instructions</li></ul>  |  |

| 4.4.1.9       Miscellaneous Instructions         4.4.1.10       Communication Support |  |

| 4.4.2 Host (Common Memory) Partition                                                  |  |

| 4.4.2 1105t (COMMON MEMOLY) Faltuloll                                                 |  |

| <ul><li>4.4.2.1 Array Accessing</li><li>4.4.2.2 Length of Arrays</li></ul>                                                      |    |

|---------------------------------------------------------------------------------------------------------------------------------|----|

| 4.4.3 Full Partition                                                                                                            |    |

| <ul><li>4.4.3.1 Quick Loading Data from the Constant Pool</li><li>4.4.3.2 Quick Field Accesses in Classes and Objects</li></ul> |    |

|                                                                                                                                 |    |

| 4.5 Partition Coverage                                                                                                          |    |

| 4.6 Summary                                                                                                                     | 60 |

| Chapter 5 Hardware Design                                                                                                       | 61 |

| 5.1 Introduction                                                                                                                | 61 |

| 5.2 Development Environment                                                                                                     | 61 |

| 5.2.1 Hot-II Development Environment                                                                                            |    |

| 5.3 Hardware Design                                                                                                             |    |

| 5.4 Java Hardware Design                                                                                                        | 66 |

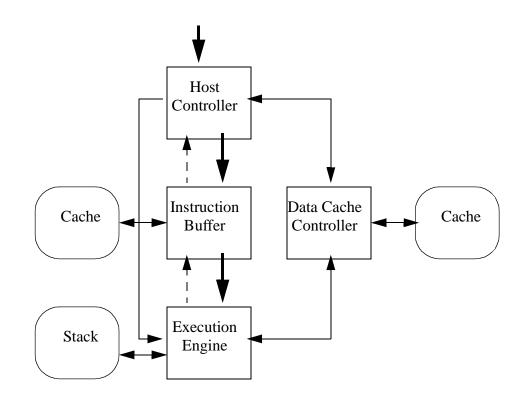

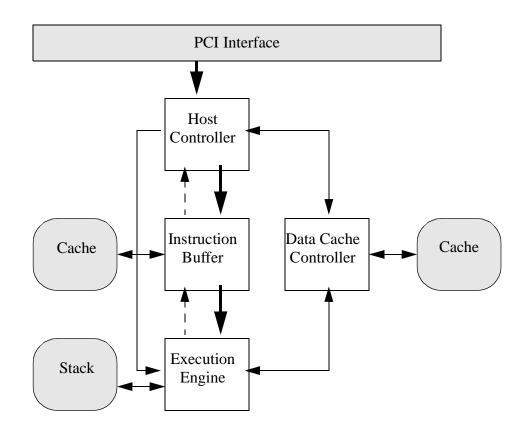

| 5.4.1 Host Controller                                                                                                           |    |

| 5.4.2 Instruction Buffer                                                                                                        |    |

| 5.4.3 Execution Engine                                                                                                          | 68 |

| 5.4.4 Data Cache Controller                                                                                                     |    |

| 5.5 Design Characteristics                                                                                                      | 69 |

| 5.5.1 Comparison to picoJava                                                                                                    |    |

| 5.6 Hardware Simulator Justification                                                                                            | 71 |

| 5.7 Software Simulator                                                                                                          | 74 |

| 5.7.1 Simulator Goals                                                                                                           | 74 |

| 5.7.2 Simulator Design Overview                                                                                                 |    |

| 5.7.3 Simulator Implementation Details                                                                                          |    |

| <ul><li>5.7.3.1 Signal Propagation</li><li>5.7.3.2 PCI Interface Model</li></ul>                                                |    |

| 5.7.3.3 Modeling Memory Caches                                                                                                  |    |

| 5.7.3.4 Primitives Enforcement                                                                                                  |    |

| 5.7.3.5 Simulator Initialization                                                                                                | 81 |

| 5.7.4 Simulator Validation                                                                                                      |    |

| 5.7.5 Execution Time Measurements                                                                                               |    |

| 5.8 Results                                                                                                                     |    |

| 5.8.1 Linear Execution Tests                                                                                                    |    |

| 5.8.2 Stack Testing                                                                                                             |    |

| 5.8.3 Instruction Buffer Testing                                                                                                |    |

| 5.8.4 Data Cache Testing                                                                                                        |    |

| 5.8.5 Remote Memory Testing                                                                                                     |    |

| 5.8.6 Results Analysis                                                                                                          |    |

| 5.9 Summary                                                                                                                     |    |

| Ch | apter 6 | Sof | tware | Design |  | 90 | ) |

|----|---------|-----|-------|--------|--|----|---|

|----|---------|-----|-------|--------|--|----|---|

| 6.1 Introduction                                    | 90  |

|-----------------------------------------------------|-----|

| 6.2 Software Design                                 |     |

| 6.2.1 Data Objects Communication                    |     |

| 6.2.2 Communication Techniques                      |     |

| 6.3 Context Switching                               | 95  |

| 6.3.1 Pessimistic Algorithm                         |     |

| 6.3.2 Optimistic Algorithm                          |     |

| 6.3.3 Pushy Algorithm                               |     |

| 6.4 Performance Analysis                            |     |

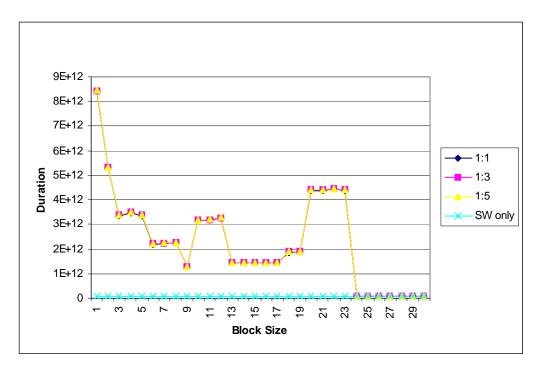

| 6.5 Results                                         | 101 |

| 6.6 Summary                                         | 106 |

| Chapter 7 Benchmark Results                         |     |

| 7.1 Introduction                                    |     |

| 7.2 Co-Designed Benchmark Results                   |     |

| 7.3 FPGA Performance Requirements                   |     |

| 7.3.1 Speed Requirements                            |     |

| 7.3.2 Space Requirements                            |     |

| 7.4 Hardware/Software Memory Requirements           | 115 |

| 7.4.1 Host Memory Accessing Requirements            |     |

| 7.4.2 Constant Pool Memory                          |     |

| 7.5 Hardware/Software Communication Requirements    |     |

| 7.6 Application Identification                      |     |

| 7.6.1 High-Level Application Characteristics        |     |

| 7.7 Summary                                         | 124 |

| Chapter 8 Conclusions                               |     |

| 8.1 Summary                                         |     |

| 8.2 Contributions                                   |     |

| 8.3 Future Work                                     |     |

| Appendix A Java Virtual Machine Bytecode Statistics | 132 |

| Appendix B Hardware/Software Partitioning           | 141 |

| Appendix C Context Switching Benchmark Results      | 151 |

| C.1 Compress Benchmark                              |     |

| -                                                   |     |

| C.2 Db Benchmark                            | 153 |

|---------------------------------------------|-----|

| C.3 Mandel Benchmark                        | 154 |

| C.4 Queen Benchmark                         | 155 |

| C.5 Raytrace Benchmark                      | 156 |

| Appendix D Co-Design Benchmark Results      |     |

| D.1 Compress Benchmark                      | 157 |

| D.1.1 Benchmark with Communication Included |     |

| D.1.2 Benchmark with Communication Excluded |     |

| D.2 Db Benchmark                            | 161 |

| D.2.1 Benchmark with Communication Included | 161 |

| D.2.2 Benchmark with Communication Excluded |     |

| D.3 Mandelbrot Benchmark                    | 165 |

| D.3.1 Benchmark with Communication Included |     |

| D.3.2 Benchmark with Communication Excluded |     |

| D.4 Queen Benchmark                         | 169 |

| D.4.1 Benchmark with Communication Included |     |

| D.4.2 Benchmark with Communication Excluded | 171 |

| D.5 Raytrace Benchmark                      | 173 |

| D.5.1 Benchmark with Communication Included |     |

| D.5.2 Benchmark with Communication Excluded |     |

| Bibliography                                | 177 |

| Partial Copyright License                   |     |

# List of Figures

| Figure 1.1 | New co-designed virtual machine architecture overview                                                      |

|------------|------------------------------------------------------------------------------------------------------------|

| Figure 2.1 | Software virtual machine execution layers of abstraction                                                   |

| Figure 2.2 | Abstract architecture for co-designed virtual machine                                                      |

| Figure 3.1 | Traditional hardware/software development                                                                  |

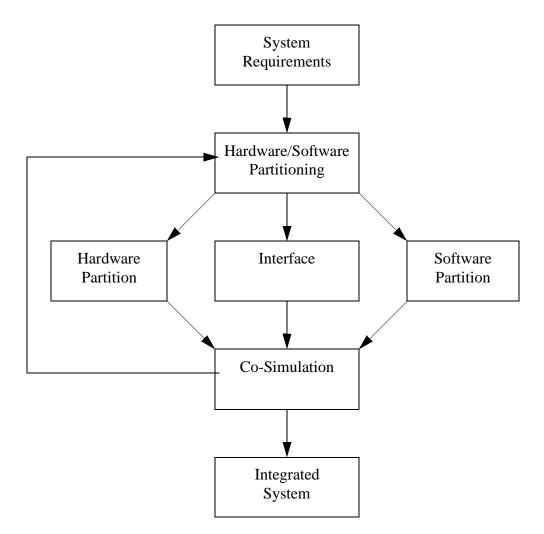

| Figure 3.2 | A conventional co-design methodology 29                                                                    |

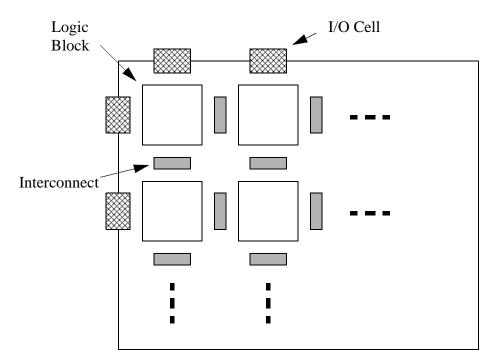

| Figure 3.3 | A conceptual field programmable gate array (FPGA)                                                          |

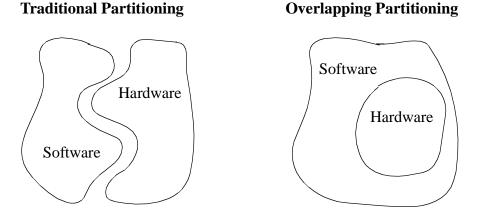

| Figure 4.1 | Abstract comparison between traditional and overlapping co-design parti-<br>tioning strategies             |

| Figure 4.2 | Abstract view of overlapping partitioning extensions52                                                     |

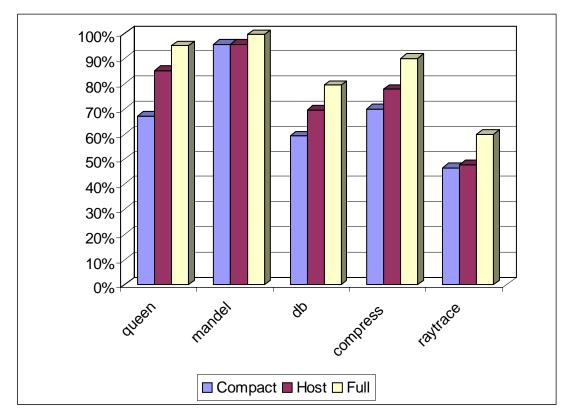

| Figure 4.3 | Instruction coverage for various partitioning schemes (based on instruction execution frequency)           |

| Figure 4.4 | Instruction coverage for various partitioning schemes (based on percentage of overall execution time)      |

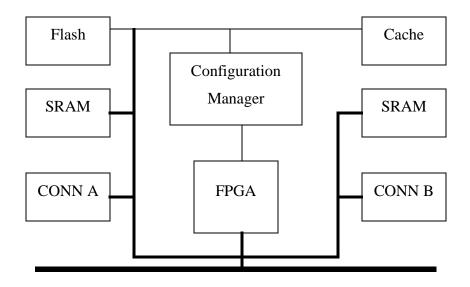

| Figure 5.1 | Hot-II development board architecture64                                                                    |

| Figure 5.2 | Java hardware architecture66                                                                               |

| Figure 5.3 | Java hardware architecture's simulated components                                                          |

| Figure 5.4 | Hardware simulator main loop of execution                                                                  |

| Figure 5.5 | Block diagram of memories available through the Xilinx Foundation Devel-<br>opment Environment             |

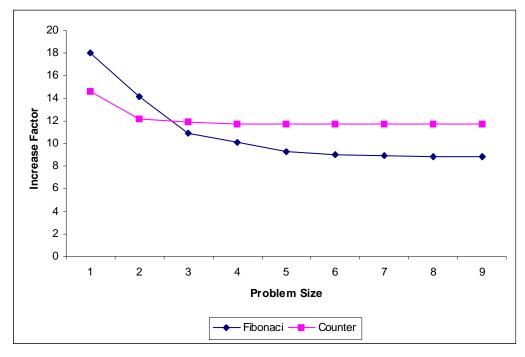

| Figure 5.6 | Performance increase of hardware architecture                                                              |

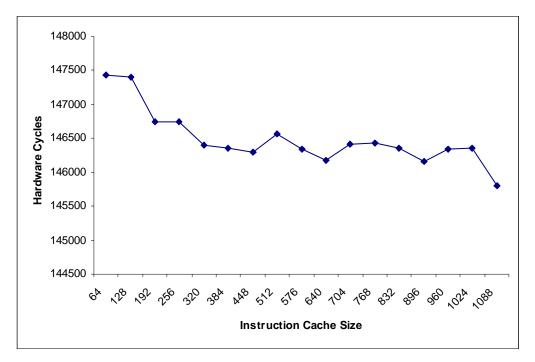

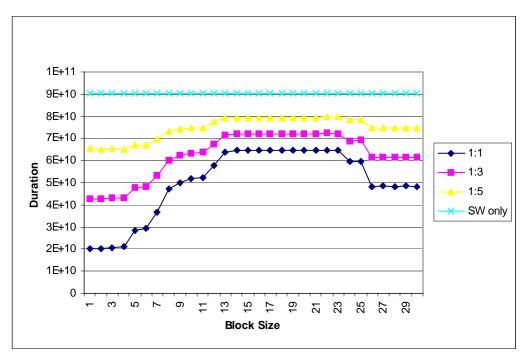

| Figure 5.7 | Affects of variable sized instruction cache in Bubble sort                                                 |

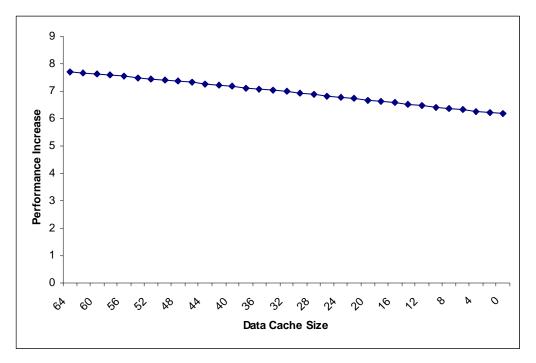

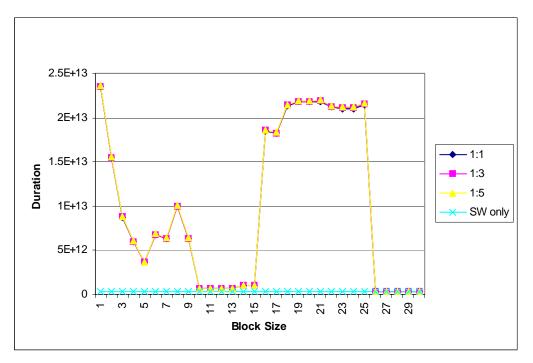

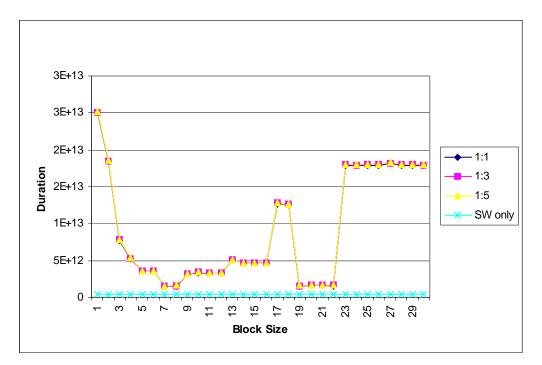

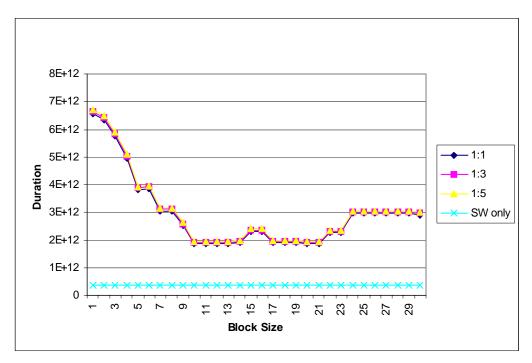

| Figure 5.8 | Performance degradation for reduced data cache size in Bubble sort88                                       |

| Figure 6.1 | Overview of interface design between hardware and software91                                               |

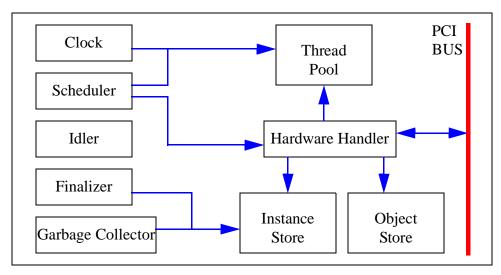

| Figure 6.2 | Software partition design of Java co-processor                                                             |

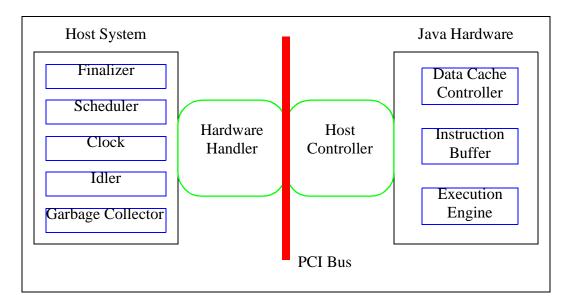

| Figure 6.3 | Overview of Java interface design between hardware and software92                                          |

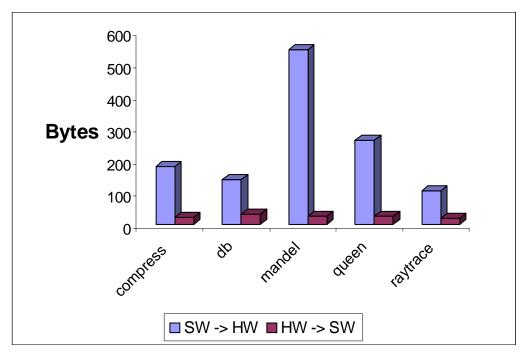

| Figure 6.4 | Average communication bandwidth used in context switching95                                                |

| Figure 6.5 | Inefficient optimistic algorithm bytecode                                                                  |

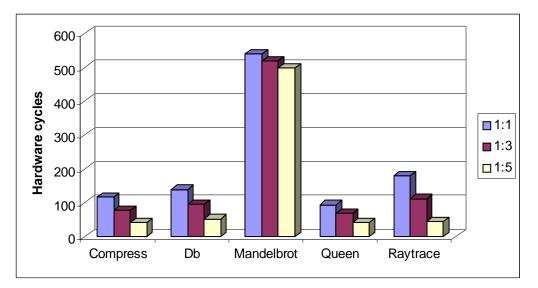

| Figure 6.6 | Required time for augmenting bytecode under each partitioning scheme in the benchmarks for block size of 1 |

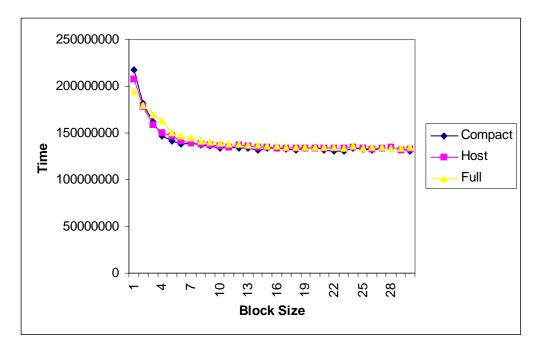

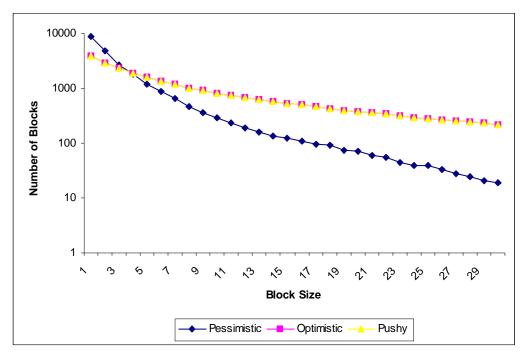

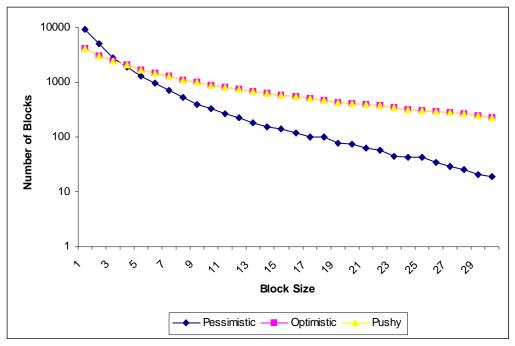

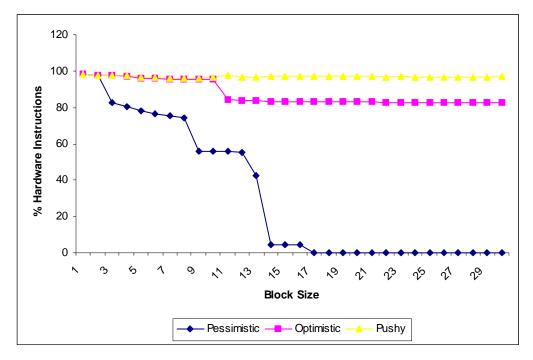

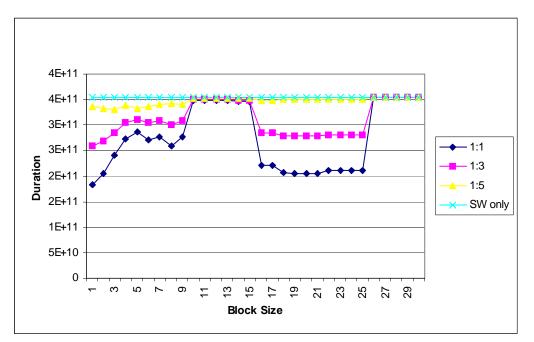

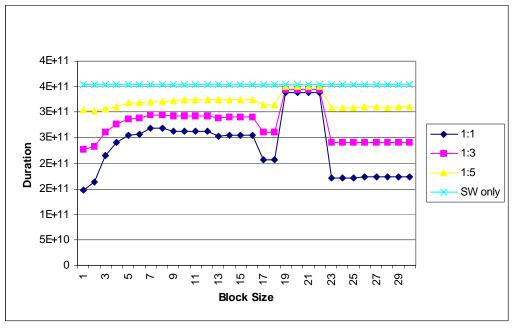

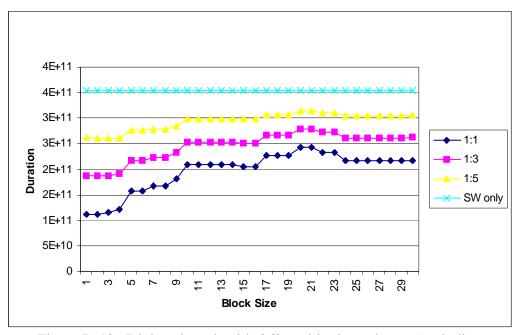

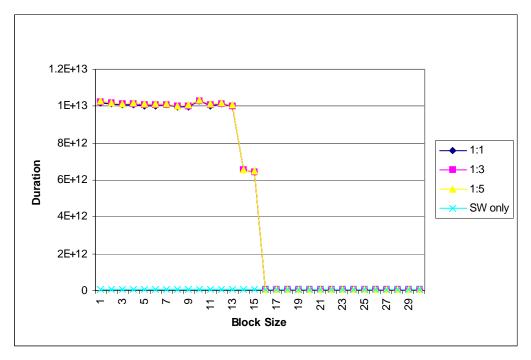

| Figure 6.7 | Mandelbrot benchmark depicting the decline in augmenting time with the decline in block size               |

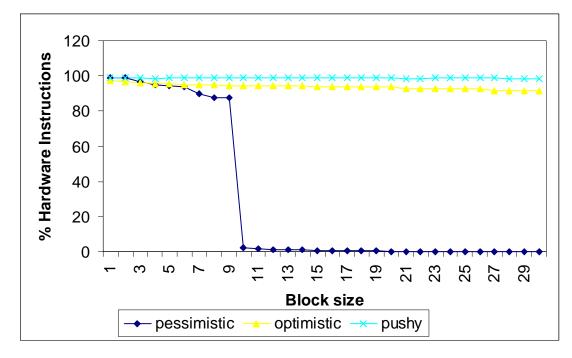

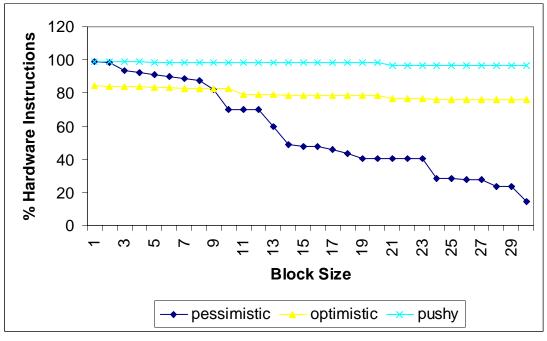

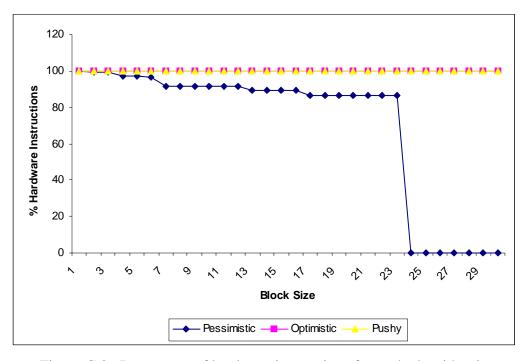

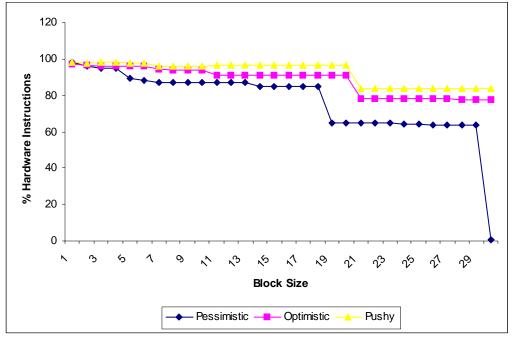

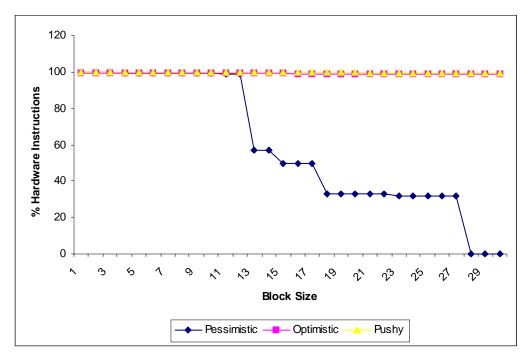

| Figure 6.8 | Mandelbrot percentage of hardware instructions                                                             |

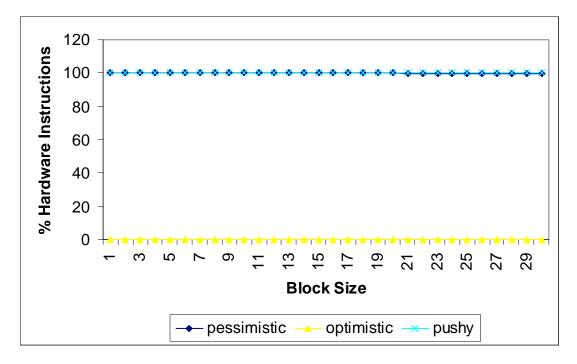

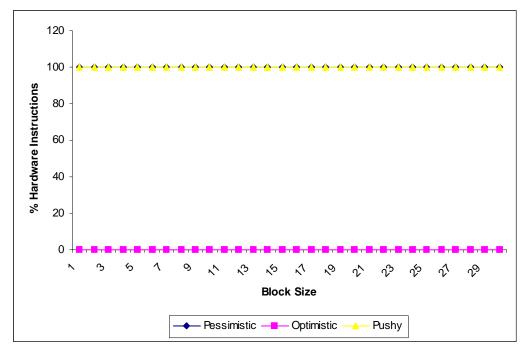

| Figure 6.9  | Jess percentage of hardware instructions                                                                                 |

|-------------|--------------------------------------------------------------------------------------------------------------------------|

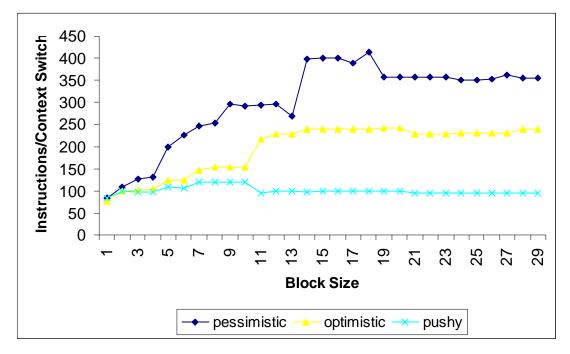

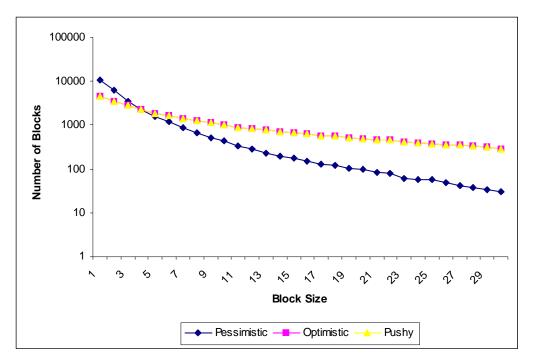

| Figure 6.10 | Average percentage of instructions/context switch 105                                                                    |

| Figure 6.11 | Average number of instructions/context switch 105                                                                        |

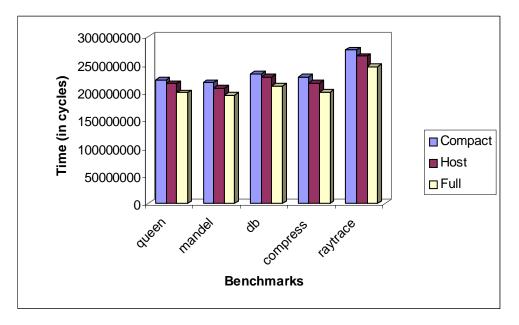

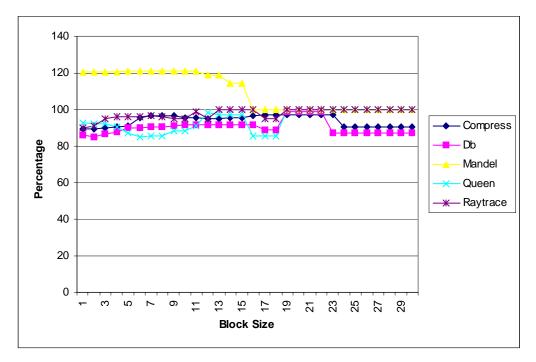

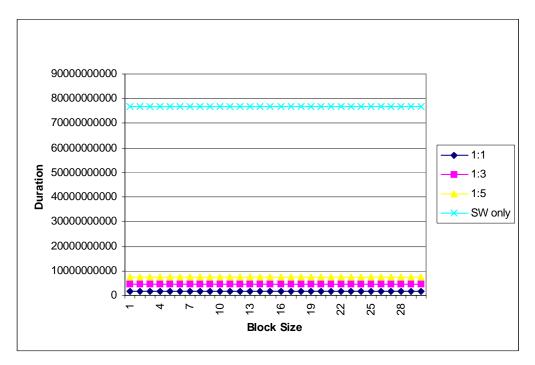

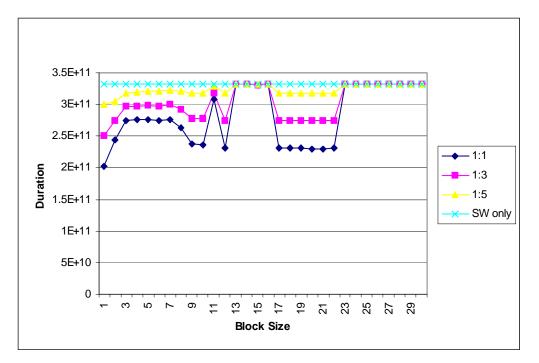

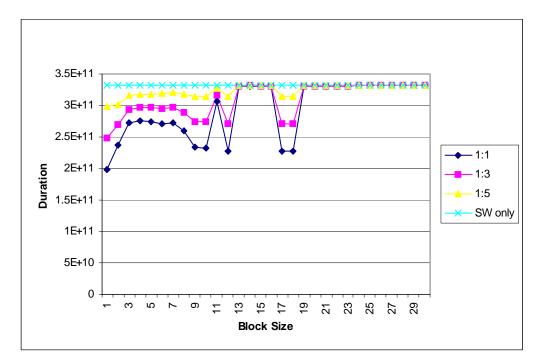

| Figure 7.1  | Benchmark results for ideal operating conditions within co-designed virtual machine                                      |

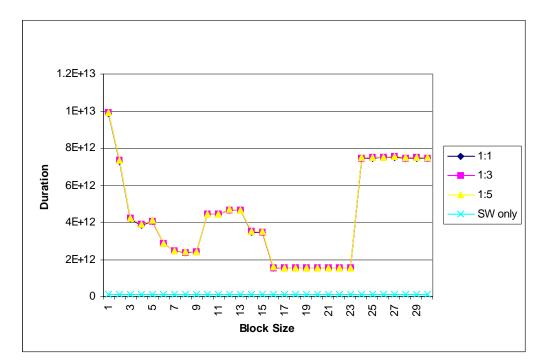

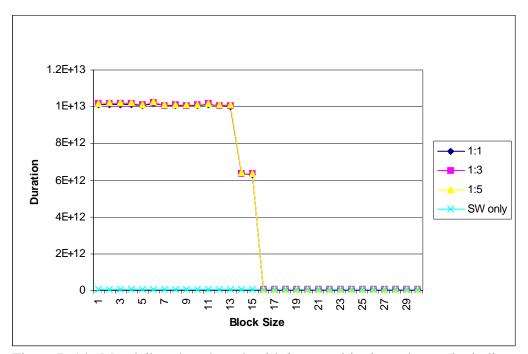

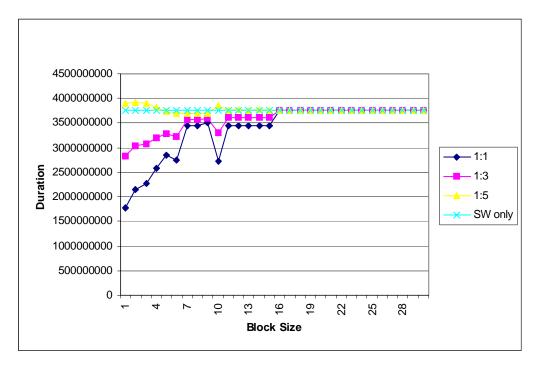

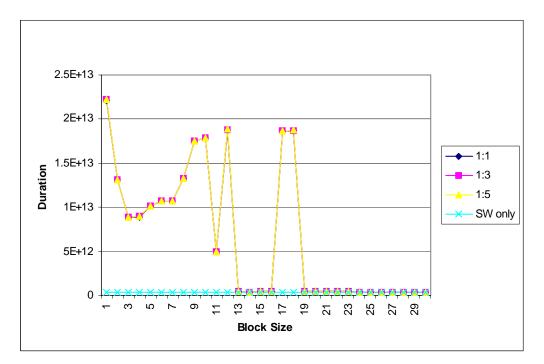

| Figure 7.2  | Co-designed virtual machine performance, including communication, with a low speed hardware component                    |

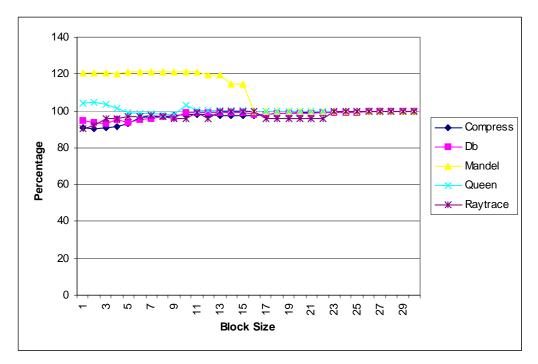

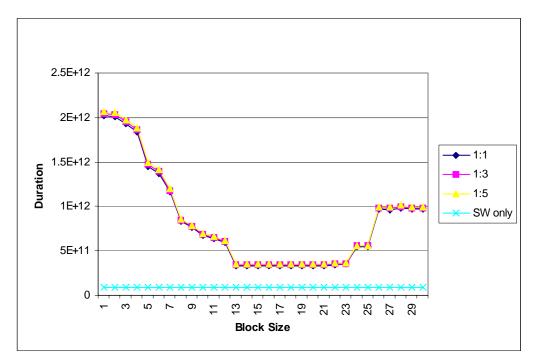

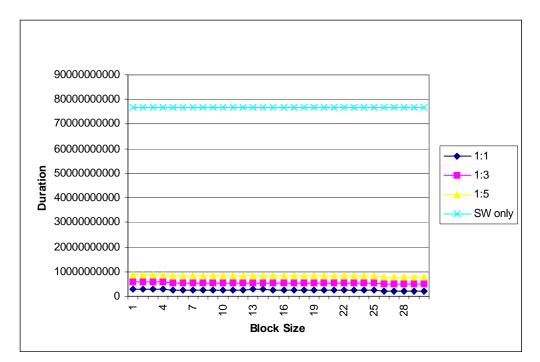

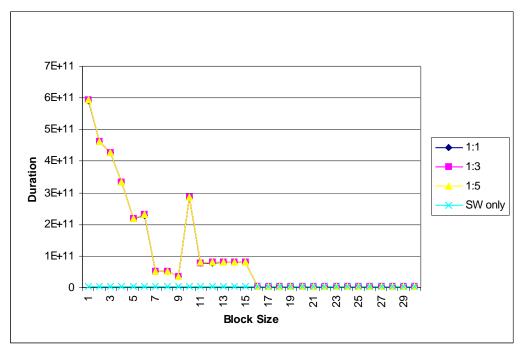

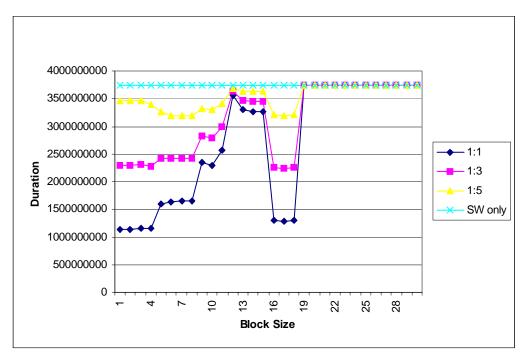

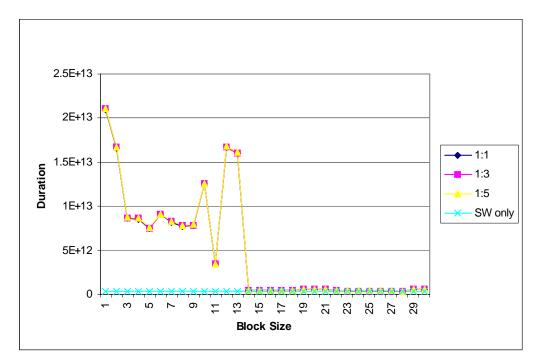

| Figure 7.3  | Host partitioning scheme performance without PCI communication costs and low speed hardware component                    |

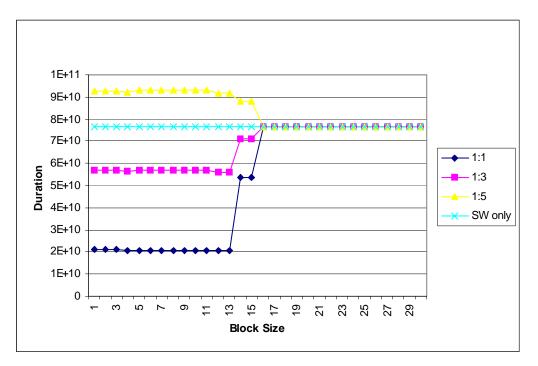

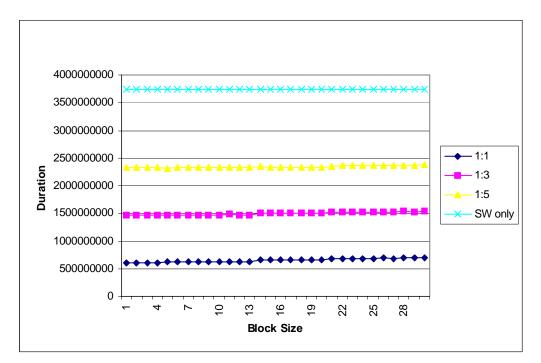

| Figure 7.4  | Compact partitioning scheme performance without PCI communication costs and low speed hardware component                 |

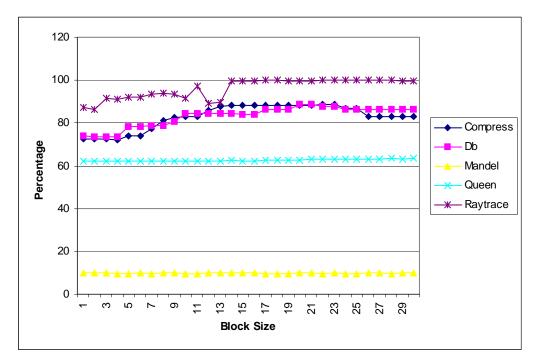

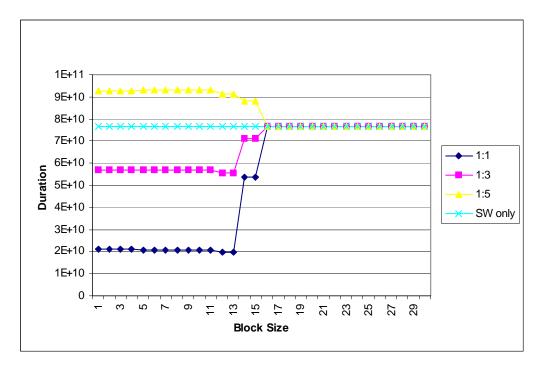

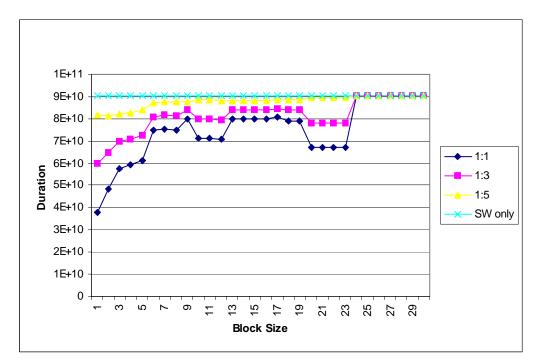

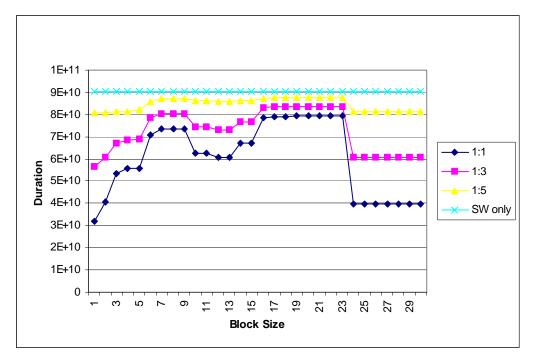

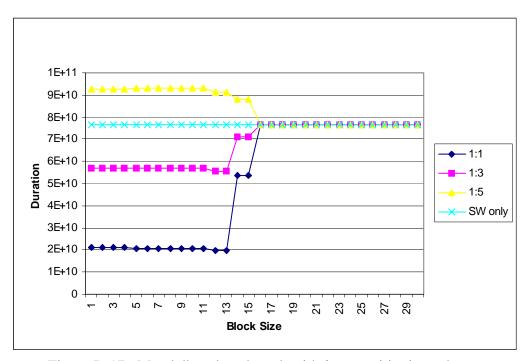

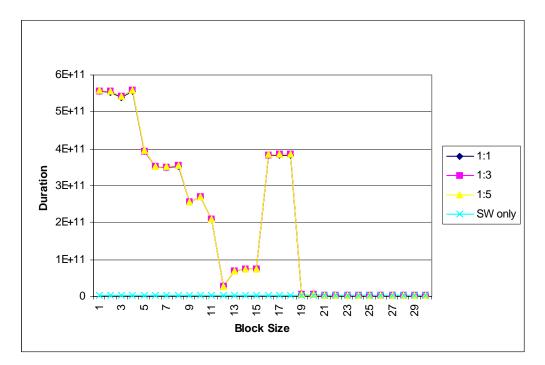

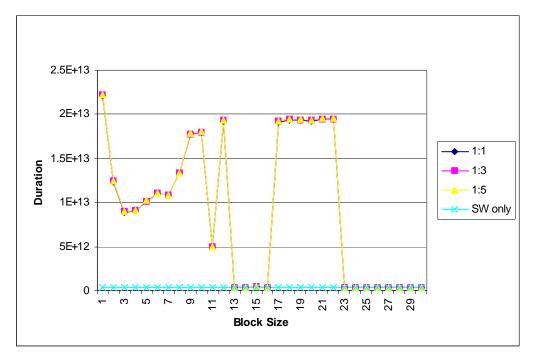

| Figure 7.5  | Co-designed virtual machine timings with no PCI communication costs,<br>under full partitioning and 1:5 clock rate ratio |

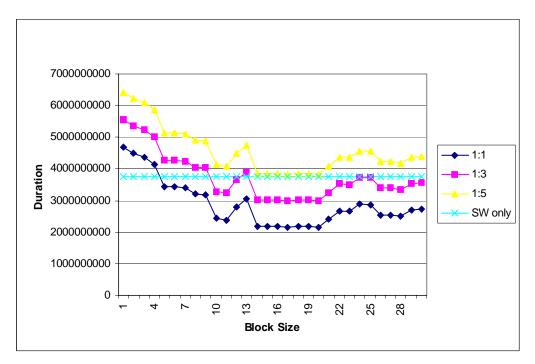

| Figure 7.6  | Mandelbrot application demonstrating effects of different raw computing speeds 113                                       |

| Figure 7.7  | Threshold values for communication delays of accessing memory from the host system                                       |

| Figure 7.8  | Critical section of Mandelbrot application 125                                                                           |

| Figure 7.9  | Critical section of Raytrace application 126                                                                             |

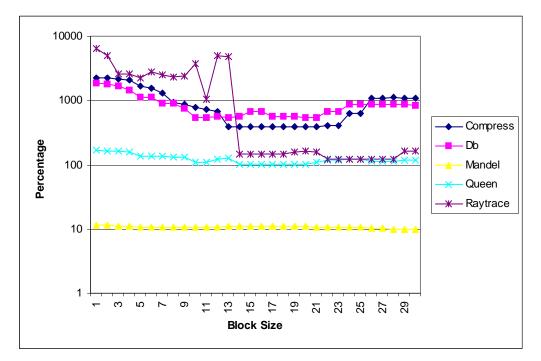

| Figure C.1  | Number of blocks for each algorithm in Compress benchmark 151                                                            |

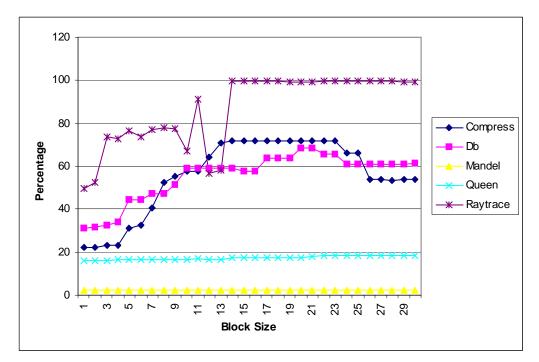

| Figure C.2  | Percentage of hardware instructions for each algorithm in Compress benchmark                                             |

| Figure C.1  | Number of blocks for each algorithm in Db benchmark 153                                                                  |

| Figure C.2  | Percentage of hardware instructions for each algorithm in Db benchmark                                                   |

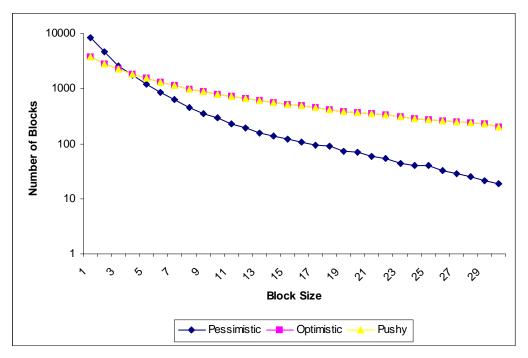

| Figure C.1  | Number of blocks for each algorithm in Mandel benchmark 154                                                              |

| Figure C.2  | Percentage of hardware instructions for each algorithm in Mandel benchmark                                               |

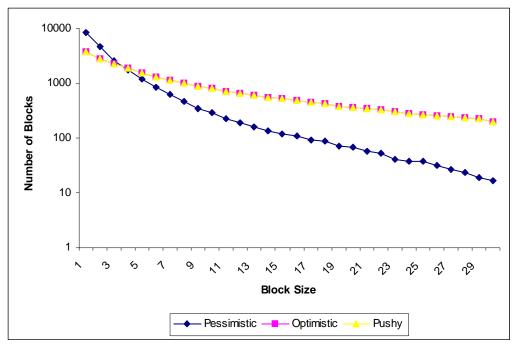

| Figure C.1  | Number of blocks for each algorithm in Queen benchmark 155                                                               |

| Figure C.2  | Percentage of hardware instructions for each algorithm in Queen benchmark                                                |

| Figure C.1  | Number of blocks for each algorithm in Raytrace benchmark 156                                                            |

| Figure C.2  | Percentage of hardware instructions for each algorithm in Raytrace benchmark                                             |

| Figure D.1  | Compress benchmark with compact partitioning scheme (including commu-<br>nication)                                       |

| Figure D.2  | Compress benchmark with host partitioning scheme (including communica-<br>tion)                                          |

| Figure D.3  | Compress benchmark with full partitioning scheme (including communica-<br>tion)      |

|-------------|--------------------------------------------------------------------------------------|

| Figure D.4  | Compress benchmark with compact partitioning scheme (excluding commu-<br>nication)   |

| Figure D.5  | Compress benchmark with host partitioning scheme (excluding communica-<br>tion)      |

| Figure D.6  | Compress benchmark with full partitioning scheme (excluding communica-<br>tion)      |

| Figure D.7  | Db benchmark with compact partitioning scheme (including communica-<br>tion)         |

| Figure D.8  | Db benchmark with host partitioning scheme (including communica-<br>tion)            |

| Figure D.9  | Db benchmark with full partitioning scheme (including communication). 162            |

| Figure D.10 | Db benchmark with compact partitioning scheme (excluding communica-<br>tion)         |

| Figure D.11 | Db benchmark with host partitioning scheme (excluding communica-<br>tion)            |

| Figure D.12 | Db benchmark with full partitioning scheme (excluding communica-<br>tion)            |

| Figure D.13 | Mandelbrot benchmark with compact partitioning scheme (including com-<br>munication) |

| Figure D.14 | Mandelbrot benchmark with host partitioning scheme (including communi-<br>cation)    |

| Figure D.15 | Mandelbrot benchmark with full partitioning scheme (including communica-<br>tion)    |

| Figure D.16 | Mandelbrot benchmark with compact partitioning scheme (excluding com-<br>munication) |

| Figure D.17 | Mandelbrot benchmark with host partitioning scheme (excluding communi-<br>cation)    |

| Figure D.18 | Mandelbrot benchmark with full partitioning scheme (excluding communication)         |

| Figure D.19 | Queen benchmark with compact partitioning scheme (including communica-<br>tion)      |

| Figure D.20 | Queen benchmark with host partitioning scheme (including communica-<br>tion)         |

| Figure D.21 | Queen benchmark with full partitioning scheme (including communica-<br>tion)         |

| Figure D.22 | Queen benchmark with compact partitioning scheme (excluding communica-<br>tion)      |

| 0 | Queen benchmark with host partitioning scheme (excluding communica-<br>tion)       |

|---|------------------------------------------------------------------------------------|

| - | Queen benchmark with full partitioning scheme (excluding communica-<br>tion)       |

| - | Raytrace benchmark with compact partitioning scheme (including communication)      |

| 0 | Raytrace benchmark with host partitioning scheme (including communica-<br>tion)    |

| - | Raytrace benchmark with full partitioning scheme (including communica-<br>tion)    |

| - | Raytrace benchmark with compact partitioning scheme (excluding commu-<br>nication) |

| 0 | Raytrace benchmark with host partitioning scheme (excluding communica-<br>tion)    |

| 0 | Raytrace benchmark with full partitioning scheme (excluding communica-<br>tion)    |

## **List of Tables**

| Table 5.1. | Ackerman function timings in clock cycles.                                                                                      | 85   |

|------------|---------------------------------------------------------------------------------------------------------------------------------|------|

| Table 5.2. | Minimal performance increase factors for each of the benchmarks based on cycle counts without consideration for clock rates.    |      |

| Table 7.1. | Threshold FPGA: Host speed ratios                                                                                               | .113 |

| Table 7.2. | Constant pool caching efficiency measurements                                                                                   | .118 |

| Table 7.3. | Percentage of original execution times with full partitioning scheme and 1::<br>FPGA:Host ratio, including communication delays |      |

| Table 7.4. | Average number of hardware cycles/context switch for each benchmark                                                             | .121 |

| Table 7.5. | Optimal performance increases under ideal conditions                                                                            | .122 |

| Table 7.6. | Instruction support and density for various benchmarks.                                                                         | .123 |

| Table A.1. | Java bytecode data collection for five benchmark applications                                                                   | .139 |

| Table B.1. | Specification of Java virtual machine instruction set between partitioning schemes.                                             | .150 |

## Acknowledgments

Many people contributed to the completion of this work. Special thanks to my supervisor, Dr. Serra. I am sure I withered away a few years of her lifespan in trying to complete this degree. To Jon, he enjoyed me as a masters student so much he recommended me to Micaela for the Ph.D. That must say something! I also want to thank Dr. Li for his help over the last few months to finish the loose ends.

To the VLSI group which suffered through many of my presentations while I gave various dry-runs for conferences and invited talks. Especially Duncan for the motivation in who will finish first. To the Graduate Students Society for having the lounge open every friday, there was no better place for escaping from the research at the end of the week. To Sean for giving me a personal demonstration of when you should stop drinking and Barry for showing me when NOT to ride a bike!

Thanks to my good buddy Gord who from rough calculations I have shared 24 kegs of beer and a few bottles of scotch with over 6 years. What else can I say but ... wow!!! No wonder people go to the bathroom so often when drinking.

Last but not least, to my family. Without their constant mocking about being under worked and a student for life, I never would have aspired to make the jump to becoming a glorified permanent student while getting paid ... a university professor :) for my family

## **CHAPTER 1**

## Introduction

This dissertation examines the merging of three problems that exist in computing today. The first problem is the slow performance of virtual machines that, with the increasing importance of the internet, have become popular for providing a homogeneous platform. The second problem is moving reconfigurable computing from the application specific domain into a new general purpose computing platform. The third problem is that of instance specific techniques used to develop hardware/software codesigned solutions to systems, in this case specifically to virtual machines. This is attributed to the complexity and variety in types of co-designed systems being developed. This dissertation investigates using reconfigurable computing in a co-designed system to alleviate some performance issues of virtual machines.

Homogeneous computing techniques have become increasingly important with the increase in internet usage and types of services. This usage continues to increase at an exponential rate [57]. A popular means by which to provide a homogeneous platform is through the use of a virtual machine. This solution is desirable since it guarantees a common platform and also allows users to maintain preferential heterogeneous hardware underneath. The drawback however is the inherent slow performance of adding another layer of abstraction between the end application and the underlying computing devices.

A tremendous amount of research has been performed into virtual machines and how to improve their performance [2,3,8,18,19,30,41,75,79,81,94,101,116]. Techniques have spanned all aspects of the execution paradigm including better source code and compilation techniques, just-in-time compilation and replacing software with hardware. Some of these techniques have provided respectable performance increases and are commonly used in virtual machine implementations, while others have not reached the mainstream. While the gap in performance has decreased, there is still a performance loss from execution on a virtual computing platform. Despite this, virtual machines are used in many contexts and applications ranging from large scale complete general purpose computing platforms to low-level specific embedded systems. Within these, a virtual machine's features and capabilities must be adjusted to reflect the support provided by and required of the environment. This work strives towards providing a full implementation of a general purpose abstract virtual machine within the context of the desktop workstation.

The implementation of the full virtual machine, as opposed to a subset of the virtual machine, is desirable since it allows a demonstration of the effectiveness of using a reconfigurable computing device in a general purpose computing platform. This raises issues such as the partitioning of the virtual machine between hardware and software, the dynamic run-time decisions for where to execute a given code segment, as well as necessary communication requirements. To reduce the problem into examining a subset of a virtual machine that exists only in hardware would remove this investigation.

There currently exist a variety of approaches to providing a computing platform such as a virtual machine. Some of these include: a dedicated hardware processor; a coprocessor specific for the platform; and a full software implementation. While each of these have their merits, they also have disadvantages. The dedicated processor and coprocessor solutions are costly if the fabricated hardware requires replacement to adapt if the virtual machine specification were to change. This is in addition to the complexities encountered in either incorporating the virtual machine support in an existing platform, or adding support for other platforms within the virtual machine itself. The software-only solution provides desirable flexibility and maintainability, but suffers in performance.

With the development of systems that incorporate both hardware and software components, there is a need for methodologies to assist the process. The tradition for hardware components has been that they are expensive and time consuming to develop. As such, traditional viewpoints have grown to the expectation that software, with its inherent flexibility, will adapt and suit the needs of the hardware resources. With the emergence of flexible reconfigurable hardware, the scope of possibilities is widened considerably.

Hardware/software co-design is the cooperative design of both hardware and soft-

ware for a specific system. Encompassing the full design process, it is concerned with many aspects such as the partitioning of the system between hardware and software through to the system integration and testing. To aid in the process, many tools, techniques, and methodologies have been proposed and examined. However due to the wide range of co-designed systems no single detailed approach or tool solution exists. There is a general process that co-designed systems follow, but it usually requires a lot of custom-izing to be applicable in practice to a diversity of systems. This dissertation focuses on hardware/software co-design for virtual machines, not for all systems.

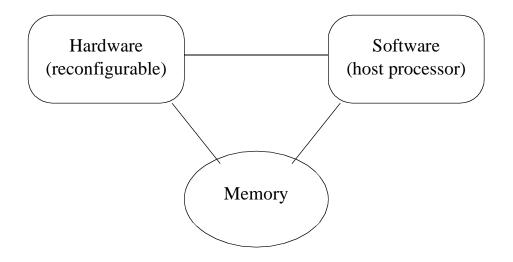

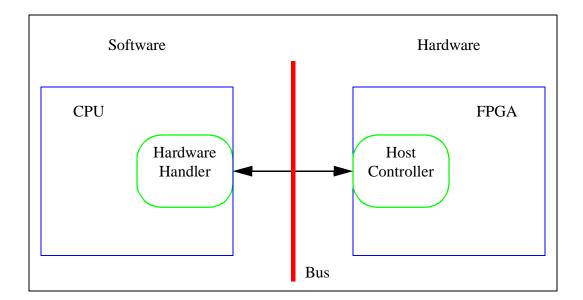

The co-designed solution here differs in that it provides an implementation that attempts to incorporate the advantages of the previous methodologies. This is accomplished by dividing cleverly the virtual machine specification between a hardware and software partition. Both of these partitions are then realized in their respective environments through the utilization of the system processor and a reconfigurable logic device. This results in a new virtual machine architecture as depicted in Figure 1.1, where each partition is supported by a different resource. The software and memory are provided through the general purpose CPU and RAM available on the local host. The hardware, however, is provided through a reconfigurable computing device.

Figure 1.1 New co-designed virtual machine architecture overview.

Reconfigurable computing is an emerging research area which utilizes programma-

ble hardware devices to provide an inexpensive custom hardware solution to a problem. Devices exist such that a user can develop a hardware design using software tools and then program the device to provide the implementation, which becomes the custom hardware. Once the hardware design is completed, the programming of the device requires only microseconds. Typically the problems addressed to date have been instance specific and narrowly focused due to the limited capabilities of the programmable devices themselves and the environments within which they exist. While the approach presented here is focused only on virtual machines, it is supportive of multiple applications executing within the platform. The previous more narrowly focused use has led to the predominant use of instance specific techniques for design and implementation of the solutions. The techniques in this dissertation attempt to be more general and can be applied to the co-design of most virtual machines.

The potential advantages of reconfigurable computing have been great enough to solicit a high level of interest [12,91]. Reconfigurable devices are being seen as a cheap alternative for custom hardware. This coupled with reprogrammability allows for quicker time to market, iterative development, and backwards compatibility. These features suggest that reconfigurable computing will only become even more pervasive in the future.

Reconfigurable computing has been used in many small application specific instances to increase performance [15,82,84]. The idea of using reconfigurable computing as an approach to solve the slow performance of virtual machines is new. Virtual machines are used to satisfy primarily the requirement of having a common platform across architectures. An immediate solution guaranteeing that a common platform exists is to simply have everyone use the same underlying hardware architecture. While this may be an ideal scenario, it is not a cost effective or feasible solution. Using reconfigurable technologies to provide a virtual machine is potentially more cost effective than the traditional Application Specific Integrated Circuit (ASIC) approach for providing a common underlying hardware architecture. Instead of *replacing* the underlying hardware with a new platform, the user simply *reconfigures* to the desired new platform [45]. While the success of such an approach to provide virtual machines is unknown, there are obvious conjectures that are interesting to explore.

This dissertation describes a different approach of computing for virtual machines through hardware/software co-design and the utilization of reconfigurable hardware, by providing guidelines and several algorithms that focus on important co-design phases of the process such as partitioning, design of the components with flexibility, and of the interface linking them together. From this research results are gathered concerning the required support for success. Included as well are performance measurements that can be attained through this solution.

### **1.1 Research Contributions**

There are three major research contributions of this dissertation and they include: an advancement towards a new general computing paradigm and architecture; a set of guidelines and algorithms for applying the general hardware/software co-design process to the specific virtual machine class of problems; and an assessment of the potential advantages of using co-design as an implementation approach for virtual machines. The remainder of this section will focus on each of these contributions and discuss them in more detail.

The first contribution is to make advances towards a new view of a general computing platform and architecture. This approach provides a computing platform which is supported by both hardware and software components through a static partitioning of instructions. By overlapping the partitions as well, a decision can be made at run-time as to the location of execution for a user application. Reconfigurable technologies to date have been focusing at the application level. This dissertation examines reconfigurable computing at the operating system and computer architecture level. This allows applications to be written without knowledge of the specialized hardware, yet receiving the benefits.

The second contribution is to outline a set of guidelines to assist in the transition of a virtual machine into this new computing paradigm, which must efficiently utilize the existing general purpose processor and the new reconfigurable resources. A significant component of this utilization is the dynamic selection of application regions to execute in the hardware partition. The partitioning scheme used to determine the opcodes that form the hardware component is critical to the outcome. Any partitioning strategy used must deal with the challenges of resource constraints, such as design space and memory, as well as implementation costs.

Co-design is new and interesting, but has been used mainly for embedded systems, where the main implementation implies having closely connected software and hardware portions and a well-defined interface. Here, a general process for co-design has been established, but the process is generic to suit all systems. This leaves the co-designer with little direction to address each of the steps within the co-design process. Steps such as partitioning become more focused only when restricted to a particular and narrow domain of application. In this research specific techniques are applied within each of the process steps for virtual machines to obtain better performance and to attempt to provide a more systematic approach to co-design, when applied to the context of virtual machines.

There are different ways of tackling this idea, for example using a co-processor, which is very successful in graphics and video streaming. In this case one utilizes a static partitioning strategy, where the hardware is used to implement specialized instructions or functionalities. Such solutions are inflexible due to the static partitioning. Likewise, the implementation using a custom ASIC co-processor also lacks flexibility, and is potentially costly. Instead the use of reconfigurable hardware can provide greater flexibility and is potentially less costly. This is reflected by the division of the virtual machines functionalities between hardware and software, the interface between the divisions, and the dynamic decision process for when to move execution between hardware and software during run-time, since the software partition maintains full functionality. Each of these concerns are addressed and the solutions can be transferred to other virtual computing paradigms. The general co-design process is described in section 3.2.

Within this approach designed for the class of virtual machines, there are several issues and ideas that are addressed and they include:

- A partitioning strategy for dividing the virtual machine between hardware and software.

- The idea of overlapping hardware and software partitions to allow for selective dynamic context switching. Three algorithms are presented and a

demonstration of the importance of context switching execution between them.

- A generic hardware design that can be adapted and manipulated for other virtual computing platforms.

- An analysis of the performance of the co-design solution as applied to the Java virtual machine.

- Lastly, a set of simulated benchmarks that quantifies the performance prediction.

The third contribution is to assess the potential performance increase of virtual machines that are implemented using hardware/software co-design dependent on the underlying hardware resources. Specifically, the Java virtual machine is used as an example. This includes an examination of the effects the physical resources of the system and characteristics of the virtual machine's applications have on the overall performance. A requirements analysis is also performed on the hardware support needed to provide a suitable environment for a co-designed virtual machine to exist. This analysis will include such factors as memory, communication, and FPGA requirements suitable for this approach to succeed.

### **1.2 Dissertation Overview**

This dissertation follows through the use of hardware/software co-design for virtual machines. A detailed discussion of the motivation for co-design and the advantages and disadvantages of this approach in comparison to other popular methods of implementation for virtual machines is in chapter two. Chapter three is a background of hardware/software co-design related information as well as reconfigurable computing and programmable hardware devices.

With the foundation set, the proposed application of hardware/software co-design to virtual machines is described in chapter four, covering the partitioning of the virtual machine between the hardware and software components. The next two chapters, five and six, discuss the hardware and software designs of the virtual machine respectively. These

designs encapsulate the interface between the partitions. Each of these chapters discusses co-design as it applies to virtual machines in general, and to the example case study of Java in particular.

Finally, chapter seven of the dissertation discusses some of the results realized through the co-design solution. This includes an analysis of some of the results obtainable through co-design as well as the requirements of the development environment. Chapter eight concludes the dissertation with a summary and a brief description of some future work that can evolve.

## **CHAPTER 2**

## Virtual Machines

### 2.1 Introduction

This chapter discusses the motivation and new concept for co-designing virtual machines clarifying the idea and context. The concept of a virtual machine, along with the advantages and disadvantages of this computing platform approach, is presented. Several common techniques for implementing virtual machines within a general purpose workstation are presented along with their advantages and disadvantages. The co-design solution proposed in this dissertation is compared and finally the chapter concludes with a discussion of the Java virtual machine (the example virtual machine that is used throughout the dissertation), and its suitability in portraying the approach.

## 2.2 Virtual Machines

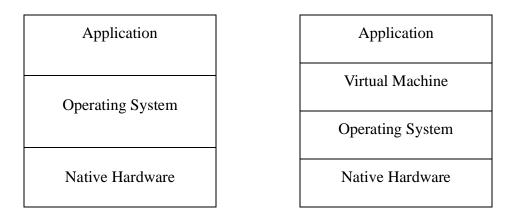

There have been many virtual machines used to support and promote different platforms of execution. The term was first introduced in 1959 to describe IBM's new VM operating system [76]. In the 1970s, a virtual machine was implemented for SmallTalk which supported a very high level object-oriented abstraction of the underlying computer [76]. A virtual machine is defined to be a self-contained operating environment that behaves as if it is a separate computer [52]. In more concrete terms, the virtual machine is a software implementation that lies between the application and the operating system. As such, it is an application that executes other applications. Figure 2.1 shows both an application running directly on top of the operating system (on the left), and an application running on top of a virtual machine.

An advantage of virtual machines over a traditional hardware architecture with an operating system is system independence. The virtual machine provides a consistent interface for application programs despite the potentially wide range of underlying hardware architectures and operating systems. This allows the application developers to provide only one software binary implementation. The key benefits include:

- Drastically reduces the costs of providing multiple versions of software across varying platforms.

- 2. Supports better application development through application portability, a uniform computing model, and a higher level of programming abstraction.

- **3.** Provides a homogeneous execution platform for distributed computing on a heterogeneous network.

- 4. Resolves issues of differing libraries and interfaces between target environments.

- 5. Provides the ability for a common security model.

There are other minor advantages such as the low cost of not having specialized hardware. For these reasons, virtual machines are a good choice to provide a homogeneous computing platform.

Figure 2.1 Software virtual machine execution layers of abstraction.

However, there is a downside to providing an execution environment as a virtual machine. Because programs running in a virtual machine are abstracted from the specific system, they often cannot take advantage of any special system features. A key example of this is the graphics capabilities where specialized acceleration for graphics at the hard-ware level is common due to the high demands placed on performance by games and

other applications. It is common today for hardware architectures to provide custom graphics support, for example the Intel processor offers *MMX* technology and AMD provides a *3DNow* instruction extension [55,1]. While both of these strive to meet the same goal, their approaches are somewhat different, and so are their interfaces to this specialized support. With applications executing within a contained virtual machine that is platform independent, the applications are prevented from accessing this support directly.

This separation of the application from the underlying system is responsible for the critical drawback of a virtual machine: its performance. Applications that execute on a virtual machine are not as fast as fully compiled applications that execute directly. The reason for this is the extra layer of abstraction between the application and the underlying hardware. Any action that is requested by an application before being executed is interpreted by the virtual machine. In addition, the virtual machine itself requires execution time to perform maintenance duties such as memory management and security checking. All of these factors contribute to the overall slow performance of applications within virtual environments.

With the increasing demand for a homogeneous computing environment, generated by the internet, and the increasing performance of computers, the use of virtual machines for computing platforms is more prominent despite some poor performance. New virtual computing platforms such as the Java virtual machine and the .NET common language runtime promote this network computing model [17].

## 2.3 Virtual Machine Implementation Techniques

There are many different approaches to implement a virtual machine. Some of the more traditional approaches are through either a software interpreter, just-in-time compilation, a dedicated native processor, or using a custom hybrid processor that was optimized to support the virtual platform [43,117]. There are also other less conventional techniques, mostly targeted for a specific application within the virtual machine and not the virtual machine itself [18]. Each of these methodologies for implementation has advantages and disadvantages. The following sub-sections outline the benefits and pitfalls

of each of these different approaches. This is followed by a description of the benefits of co-design, which presents the co-design solution to be an alternative for the desktop workstation environment.

#### **2.3.1 Software Interpreter**

A software interpreter is the most common form of implementation for a virtual machine. A driving force behind this is that software meets the common demands and features desired of a virtual machine. Typically virtual machines are "virtual" because users desire to have portability across different hardware platforms, want a cheap platform, and require backward compatibility as the platform grows into a more stable environment. A software computing platform has traditionally been the most appropriate means by which the implementation can be realized to satisfy these requirements.

The software implementation is the cheapest and quickest means by which the virtual machine can evolve from concept, through prototyping and research, into an end product. The currently popular Java virtual machine is an example of this evolution. It originally began as a platform for cable TV switchboxes and continually developed and grew into the general purpose computing platform that it is today [24]. Currently the Java platform, since first released as a general purpose computing platform in 1995 has undergone four major revisions and numerous other minor editions [103]. Software provides suitable features for this evolution mainly through its vast set of cheap development tools and flexibility with underlying hardware architectural platforms. The flexibility that software provides for analyzing the virtual machine in terms of configurability provides insights to help develop efficient and suitable implementation ideas. This flexibility is also invaluable when the virtual machine has not matured and is changing through continuous revisions. Having the ability to easily update and release a new version is important during this stage of the virtual machine's life cycle.

Unfortunately, this is the point where software-based implementation becomes a burden on the end virtual machine. A software interpreter is a great mechanism for developing and analyzing the virtual machine, however, its lack of performance hinders the virtual machine from being used for computing intensive applications. The extra layer of interpretation in execution is too costly in performance. As can be seen from Figure 2.1, with a software implementation of the virtual machine, there is the extra layer of abstraction above the host operating system. This extra layer, while providing a standard interface to the underlying hardware, also forbids access to any special capabilities of the operating system or hardware architecture. In a typical application developed for the hardware platform, the virtual machine layer does not exist. Instead, the application has more direct access to the hardware and its special capabilities. There are also advantages of this abstraction level, as it also acts as a "sandbox", protecting from illegal access to other applications and preventing the host operating system from crashing as a result of the virtual machine application [72].

For performance, this raises even greater concerns when the operating system is capable of multi-tasking, as it can also result in worse performance as the operating system is sharing the hardware resources with other applications, possibly equal in priority to the virtual machine itself.

#### 2.3.2 Just-In-Time Technology

A common technique that has been used to increase the performance of software implementations for virtual machines is that of just-in-time (JIT), or hot-spot, compilers. This technique utilizes the fact that a significant amount of the time during execution is spent executing a small fragment of the overall application. This technology attempts to identify these fragments of the application during runtime and compile them into native code, thus allowing the application to perform faster since it can avoid software interpreting and execute natively [94,103]. Given the correct code fragments of the application to JIT, the application can almost become a native application. This technique has shown high levels of performance increase for many virtual computing platforms [103,94].

There are several challenges that just-in-time technologies face. Two factors are identification of the time critical regions of the application and compilation of the virtual platform code to execute in the native architecture. Identifying the time critical sections of an application is difficult since it is dependent on the specific application and requires monitoring the application during execution. Some of the original Just-in-Time compilers used for Java attempted to compile all of an application methods during loading, but this resulted in large memory requirements and in compilation of code that is sometimes

only used once [119]. Moreover, depending on the input to a given application, the time critical sections can change. Finally, once identified, compiling the time critical sections of the application into native code is often a challenging task. This is especially true when the virtual and native machines differ significantly in architectures. Manipulating the application to represent it in the supported native instruction set can present a problem [94]. All of this effort must be performed quickly, as time spent performing the just-in-time compilation weighs against the performance gains obtained.

#### **2.3.3 Native Processor**

When a virtual machine is in high use and performance is of primary importance, it is common for the platform to become native. For this, a custom processor is developed based on the instruction set of the virtual platform. This contributes towards providing higher performance capabilities for the platform's applications. A key trade-off for this performance is the loss of flexibility as well as performance for other computing languages and paradigms [20]. With a native processor, there is less flexibility. Customizing the platform while keeping the proper backwards compatibility. Customizing the architecture for a specific computing platform or language also causes problems for executing other platforms and languages. An example of this is the recent picoJava processor [19,27]. While the specific processor does provide performance gains over software emulation, the performance of other computing platforms, such as the execution of C programs, suffers because the Java specific platform does not offer suitable features as would another general purpose processor [20].

Another concern that arises from having a native processor for the virtual machine platform is the support of other platforms. One reason for having various platforms is because each platform offers different features and capabilities. Using a native processor may include the features that are desirable for one platform while losing the necessary characteristics for another. Changing the native processor may be suitable for a dedicated environment, but not for a general purpose environment where the native processor must meet a common ground between all supported platforms. In the context of this research, namely a desktop workstation, the use of a native processor for the targeted virtual machine is not considered desirable. There are many examples of virtual platforms becoming actual hardware platforms, such as the Lisp machine, the Pascal processor, and other computer architectures for such languages as Algol and Smalltalk [39,105,92,22,90,51,77]. Each of these language specific platforms is capable of providing performance increases simply because the architecture is targeted to the language and its computing paradigm. For example, the Lisp machine utilizes the fact that the language is stack based, and hence so too is the architecture. This is also true for more current and emerging computing platforms such as Java [2,95,99,58,65,117]. These specific examples, despite their demonstration of a performance increase over software implementations, have not been adopted as common place solutions. One contribution to this outcome is the high costs associated with specialized hardware. In most cases, there is not a sufficient demand for performance on these platforms to warrant the costs.

#### 2.3.4 Hybrid Processor

A hybrid processor attempts to provide greater performance for multiple platforms by providing a native processor that is based on the combination of the platforms merged together. This approach in theory provides the best of all the incorporated platforms to accelerate execution for each virtual machine [29,33]. There has been considerable research into hybrid processors to specifically enhance the support of Java execution [3,4,8-10,30-32,79,80]. There are, however, some drawbacks with this approach. Incorporating multiple virtual machines can result in a very complex design that may be very challenging to implement. Such factors as design space and cost also arise, sometimes making this approach impractical.

Having each platform directly supported in the underlying native processor may lead to increased performance. Again, several drawbacks may mitigate against performance gains. There exist many different platforms with many different philosophies that are not always compatible. Trying to incorporate platforms with a mix of philosophies can result in a system where each platform is hindered by the other(s). With the vast number of platform architectures, it is probable that the platforms will have conflicting features. Having the scenario of compromising the performance of one platform to improve another is never desirable and often intolerable.

### **2.4 Co-Designing Virtual Machines**

The previous section described several methodologies commonly used to implement a virtual machine: pure software based, and pure hardware based, with both native and hybrid instruction sets. Each of these methodologies has its benefits and its costs. This section instead discusses the idea of co-designed virtual machines using a reconfigurable device.

Virtual machines are typically software implementations of a hardware architecture plus supporting software management or operating system. Backward compatibility, cost, and portability issues are common reasons for providing a platform as a virtual machine. By having the specified machine in software it can be cheaply implemented and run on top of, without affecting, many existing host platforms. The motivation behind codesigning a virtual machine is to increase the performance of the virtual machine's execution through hardware support. In this dissertation, the hardware support is provided through the use of a reconfigurable hardware device, namely a Field Programmable Gate Array (FPGA).

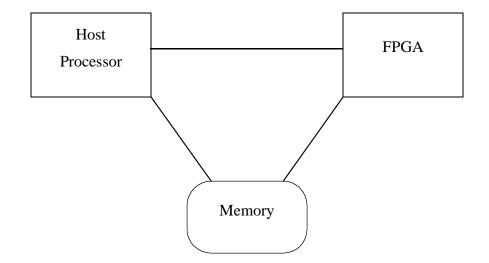

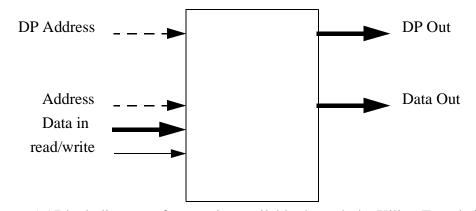

There are two parts that make up a virtual machine: a low-level instruction set, and a high level operating system. The idea of co-designing virtual machines is based on supporting each part of the virtual machine by the most desirable approach. Thus, providing the low-level instruction set of the virtual machine in hardware, i.e. the FPGA, and the high level operating system in software, i.e. the host processor, is desirable. For the codesigned solution, an abstract depiction of the conceptual architecture for implementation is depicted in Figure 2.2.

This architecture is seen as desirable as each part is delivered through technologies that provide a high level of performance while still maintaining flexibility. The co-design approach, though simple in concept, faces the new challenge of integrating the hardware and software components. This requires the careful design of the interface between them. Architecturally, both of these computing elements are connected via buses to the memory unit, and to each other. Ideally, there are three separate buses, but sharing a common bus is possible. This allows for close shared execution between the two devices on one execu-

Figure 2.2 Abstract architecture for co-designed virtual machine.

tion task.

There is the issue of a bottleneck caused by the accessing of the memory region by both the FPGA and the host processor. This can result in a significant issue which is not addressed here in detail. Chapter 7 does however consider the effects of memory accessing bandwidth, as well as other hardware architectural features.

This approach was used in the past, but mainly for specific processing purposes and not for a general computing virtual machine [64]. Configurable computing has been broadly used in embedded computing and telecommunications to address such problems as high-speed adaptive routing, encryption and decryption, and cellular base station management [68]. The co-design idea here is to implement a portion of the virtual machine in hardware using reconfigurable hardware technology [62], i.e. a more general problem.

While the idea of using reconfigurable hardware for application acceleration or for providing an embedded system platform is not unique, using reconfigurable hardware within the desktop workstation to support virtual computing platforms is rather novel. This concept is intriguing since the same hardware resources can be used for not just one virtual platform, but for several virtual machines, or for any other process. The ability to reconfigure the underlying hardware to specifically support the computing platform offers many advantages. Most importantly, this paradigm for computing may provide a solution

to the performance problem of software based implementation virtual machines.

For this to be viable, a co-design flow needs to be developed to assist the implementation. There exists a general co-design process, but it is too general for virtual machines. There is little direction provided to assist in how to partition the virtual machine, how to design the hardware and software components, or what comprises the interface between them. While assistance for these stages may not be possible for all co-designed systems in general, it may be possible for virtual machines as a class of problems. Currently, there exists no assistance for this class of problems beyond the support available for codesigned systems in general, or for embedded systems more narrowly focused in a domain. This dissertation will address this problem, by presenting techniques and guidelines that can be used specifically for directing the co-design of virtual machines. The next section discusses in depth the foreseen benefits of a co-designed virtual machine.

### 2.5 Benefits of a Co-Designed Virtual Machine

A major benefit of any implementation approach for virtual machines is the ability to change and extend the implementation for revisions to the virtual machine's specification. The use of a co-designed virtual machine promotes this flexibility through the reconfigurability of the hardware architecture. Revising the implementation is arguably no more difficult than that of changing a full software implementation. This is not the case however, when a dedicated ASIC co-processor or hybrid processor is used. In these instances, changing the hardware can be a high cost venture. The recent Java virtual machine is an example of this. From a software implementation of the virtual machine, the Java platform has undergone four major and several minor implementation revisions, the specification of the virtual machine itself has been revised once, and the Java processor, picoJava, has undergone a major revision as well [103,72,109,99]. This demonstrates the importance of having a flexible implementation that can be easily changed to accommodate revisions in the virtual machine.

When using a hardware device to provide a service there is always a concern regarding availability. Even if a hardware device exists to provide the service desired, is

the device suitable for the user? Assuming a custom ASIC co-processor were available, one needs a different type for each different type of virtual machine. It could be envisioned that the host system would contain a general purpose processor along with several dedicated co-processors on the system mainboard. Is the computing platform for each of these dedicated co-processors used often enough to justify having dedicated hardware resources? This is especially true if the performance demand for a particular virtual machine is low, thus causing a high cost for hardware support. For a dedicated ASIC coprocessor or hybrid processor solution this can be an issue. Using reconfigurable hardware, the same hardware can be used to support multiple computing platforms, thus amortizing the cost of having this hardware. The cost associated with having a reconfigurable device is much less dramatic when several computing platforms can be supported. It can be envisioned that as each virtual machine is requested by an application, the system will reconfigure the hardware to the appropriate virtual machine and then execute. Thus, only one general processor and one reconfigurable device can theoretically support an unlimited number of virtual machine types. Moreover such reconfigurable coprocessor can support any number of other configurations for any other application.

Cost is always an issue raised when discussing the value of various means of implementation. This is a rather subjective area to argue when discussing the effort involved to fulfill the implementation. Past research experience shows that a software implementation is easier than a hardware implementation because of its flexibility, so a software and JIT solution would potentially be easier to complete than a co-designed solution. The codesigned solution, however, is arguably easier to implement than the hybrid solution which requires integration with a secondary computing platform, and the dedicated coprocessor which involves fabricating the solution.

Often, a computing platform is supported through a virtual machine because it has an embedded architecture that differs from the native architecture. To attempt to merge the two computing platforms together to support both paradigms is a very challenging and often counterproductive process. Some platforms simply cannot be easily merged based on their underlying fundamental architectures. The co-designed solution avoids this by having the embedded architecture of the virtual machine supported within its own computing element. This allows the hardware support for the virtual machine to be optimized for its platform, without compromising support for another. This is an advantage that the co-designed solution provides over the hybrid processor.

The just-in-time compiler solution in some sense performs the complement of the co-designed approach. The JIT technology transforms the application from the virtual machine instruction set to the native instruction set of the host processor. Conversely, the co-designed approach changes the native instruction set to make the application native. In this sense the co-designed virtual machine has the advantage that the transformation takes place at compile-time when the reconfigurable device is programmed, while the JIT transformation takes place at run-time after the time critical section is identified.

When providing a virtual machine through a software emulation environment, the time critical section of the virtual machine is optimized to take advantage of the underlying hardware architecture to improve performance. When examining the software implementation of the Java virtual machine, it can be seen that the time critical loop of fetching and executing instructions is optimized specifically for each hardware platform [103]. It has both Sparc and Intel architecture modules for that specific component of the virtual machine. This adds complexity when providing the virtual machine through a new platform as this module is customized for the new underlying hardware architecture. Often the hardware component of the co-designed virtual machine, which is provided through reconfigurable logic, overlaps the platform specific components of the software only solution. In this case, a significant portion of the platform dependencies are removed. With less need to port platform dependent implementation components of the virtual machine between platforms, the porting process becomes much simpler. Thus, when a virtual machine is co-designed for one general desktop platform it can more easily be manipulated for all desktop platforms.

In some aspects, the co-processor solution and the co-designed approach are very similar. Both provide additional hardware resources that target specific needs of a computing platform to improve the performance. There are however, three main differences that separate these approaches. First, the co-designed solution discussed here utilizes reconfigurable technology. This reduces the cost of hardware resources and allows support for multiple virtual machines as discussed previously. Secondly, the co-processor is designed to work as an add-on to the general purpose processor. Control flow is dictated by the CPU and the co-processor just performs fine grained tasks that are requested of it. The co-designed approach views the added hardware support as an equal processing unit and as such it contributes to the control flow of an applications execution. This does how-ever add complexity to the design that may be unnecessary. Thirdly, the co-designed solution goes beyond simply providing additional hardware support, but addresses the synergy between the added hardware support and the whole virtual machine. This is seen later in the dissertation in the discussion of what support to provide in hardware/software, where to execute a block of instructions, and how to design the software to work seamlessly with the hardware support. In a typical co-processor, these issues are not addressed and instead the design focuses on providing just a standard interface to the co-processor.

Finally, a major benefit of the co-designed solution is the use of two computing devices. With the addition of a hardware device, it is now possible to execute two flows of execution simultaneously. In the simplest of circumstances, this can execute a virtual machine application and arbitrarily any other application in parallel. If however the virtual machine being used supports multi-threading, this can result in two threads within the virtual machine executing in parallel. This can result in a further performance gain, but is not addressed in this dissertation.

#### 2.6 Java Virtual Machine

For this research on co-designing virtual machines, it is as important to show the application of the approach to a case study virtual machine as it is to describe the approach itself. While all of the ideas are applicable to virtual machines in general, the use of a concrete virtual machine allows for some insight into the potential performance that can be gained through co-design. The use of a case study is also beneficial in examining some of the more detailed aspects of the co-design approach and from that abstracting the results to form some additional general guidelines to follow in the process. For this, a case study virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and it was decided to use the Java virtual machine must be chosen and the process.

tual machine. That is, the Java virtual machine as within the desktop environment and not that of a Java platform for use in embedded computing [104,60,69]. While both targets share some similar problems, they both contain issues that are unique to their usage [74,78,83].