# PARALLEL IMPLEMENTATIONS OF SELECTED IMAGE PROCESSING TECHNIQUES

by Christopher Turner

TR93-077 May 1993

This is an unaltered version of the author's M.Sc.(CS) Thesis

Faculty of Computer Science University of New Brunswick P.O. Box 4400 Fredericton, N.B. Canada E3B 5A3

> Phone: (506) 453-4566 Fax: (506) 453-3566

# Abstract

In this thesis we present parallel implementations of one local (convolution) and one global (regular moment extraction) image processing technique on a multi-transputer system. Issues relevant to implementation design, including computational algorithm selection, initial data pass, and topology selection are discussed. Linear speedups in the convolution implementations are observed whereas the efficiency of the regular moment programs decreases as the number of transputers increases. Analysis of the implementations including parallel time complexity functions and observations about data passing and topology selection is given. Two theoretical performance models based on the implementations closely match empirical timing results.

# Contents

| A  | bstra          | ıct     |                       |     | ii   |  |  |  |  |  |  |  |  |  |

|----|----------------|---------|-----------------------|-----|------|--|--|--|--|--|--|--|--|--|

| Li | st of          | Table   | <b>es</b>             | ,   | viii |  |  |  |  |  |  |  |  |  |

| Li | ist of Figures |         |                       |     |      |  |  |  |  |  |  |  |  |  |

| A  | ckno           | wledge  | ements                |     | хi   |  |  |  |  |  |  |  |  |  |

| 1  | Inti           | roduct  | ion                   |     | 1    |  |  |  |  |  |  |  |  |  |

|    | 1.1            | Thesis  | s Objective           |     | 2    |  |  |  |  |  |  |  |  |  |

|    | 1.2            | Strate  | egy                   |     | 3    |  |  |  |  |  |  |  |  |  |

|    | 1.3            | Thesis  | s Structure           | • • | 3    |  |  |  |  |  |  |  |  |  |

| 2  | Par            | allel P | Processing            |     | 5    |  |  |  |  |  |  |  |  |  |

|    | 2.1            | Introd  | duction               |     | 5    |  |  |  |  |  |  |  |  |  |

|    | 2.2            | Parall  | lel Architectures     |     | 6    |  |  |  |  |  |  |  |  |  |

|    |                | 2.2.1   | Data Streams          |     | 6    |  |  |  |  |  |  |  |  |  |

|    |                | 2.2.2   | Instruction Streams   |     | 6    |  |  |  |  |  |  |  |  |  |

|    |                | 2.2.3   | Memory Type           |     | 7    |  |  |  |  |  |  |  |  |  |

|    |                | 2.2.4   | Communication Method  |     | 7    |  |  |  |  |  |  |  |  |  |

|    | 2.3            | Parall  | lelization Techniques |     | 8    |  |  |  |  |  |  |  |  |  |

|    |                | 2.3.1   | Data Parallelism      |     | 8    |  |  |  |  |  |  |  |  |  |

|     | 2.3.2   | Instructional Parallelism                     | 8  |

|-----|---------|-----------------------------------------------|----|

|     | 2.3.3   | Processor Farming                             | 8  |

| 2.4 | Terms   | and Definitions                               | 9  |

|     | 2.4.1   | Speedup                                       | 9  |

|     | 2.4.2   | Efficiency                                    | 9  |

|     | 2.4.3   | Parallel Processor Cost                       | 10 |

|     | 2.4.4   | Granularity                                   | 10 |

| 2.5 | Transp  | outers                                        | 11 |

|     | 2.5.1   | Communicating Sequential Processes            | 11 |

|     | 2.5.2   | Transputer Networks                           | 11 |

|     | 2.5.3   | The IMS T800 Transputer                       | 12 |

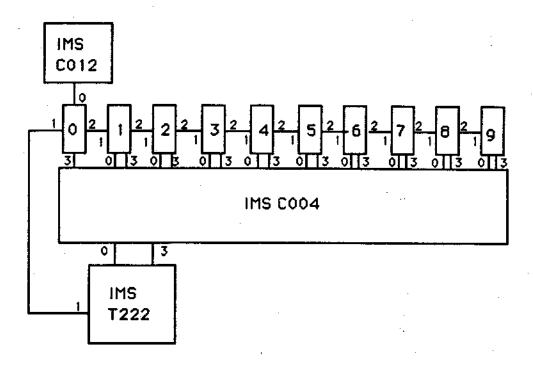

|     | 2.5.4   | The IMS C012 Communication Device             | 12 |

|     | 2.5.5   | The IMS C004 Link Switch                      | 12 |

|     | 2.5.6   | The IMS T222 Network Configuration Transputer | 13 |

|     | 2.5.7   | The IMS B008 Motherboard                      | 13 |

|     | 2.5.8   | The IMS T9000 Transputer                      | 13 |

|     | 2.5.9   | Optimal Transputer Programming Model          | 14 |

| 2.6 | Paralle | el ANSI C                                     | 16 |

|     | 2.6.1   | Source Files                                  | 16 |

|     | 2.6.2   | Configuration Source Files                    | 17 |

|     | 2.6.3   | Program Compilation and Execution Processes   | 17 |

| 2.7 | Remai   | rks                                           | 18 |

| -   | _       |                                               | 90 |

|     | •       | 8                                             | 20 |

| 3.1 |         |                                               | 20 |

| 3.2 | Digita  | Representation of Images                      | 21 |

| 3.3 | Image   | Processing Equipment                          | 22 |

|     | 221     | Camerae                                       | 22 |

|   |     | 3.3.2    | Digitizers                        | 3 |

|---|-----|----------|-----------------------------------|---|

|   |     | 3.3.3    | Monitors                          | 3 |

|   | 3.4 | Image    | Processing Systems                | 3 |

|   |     | 3.4.1    | Need for Parallel Processing      | 3 |

|   |     | 3.4.2    | Our Multi-Transputer Based System | 3 |

|   | 3.5 | Convo    | lution                            | 5 |

|   |     | 3.5.1    | Algorithm                         | 5 |

|   | 3.6 | Mome     | nts                               | 6 |

|   |     | 3.6.1    | Moment Invariants                 | 7 |

|   |     | 3.6.2    | Algorithms                        | 8 |

|   | 3.7 | Remai    | rks                               | 4 |

|   | a.  | ١ ٣٠     | T 7                               | _ |

| 4 |     | -        | nsputer Implementations 3         |   |

|   | 4.1 | Introd   | uction                            | 7 |

|   | 4.2 | Progra   | umming Technique                  | 8 |

|   | 4.3 | Convo    | lution                            | 8 |

|   | 4.4 | Regula   | ar Moments                        | 9 |

|   | 4.5 | Remai    | rks                               | 4 |

| 5 | Mni | lti-Trai | nsputer Implementations · 4       | 6 |

| • | 5.1 |          | uction                            |   |

|   | 5.2 |          |                                   |   |

|   |     | •        | <b></b>                           |   |

|   | 5.3 |          | al Issues and Strategies          |   |

|   |     | 5.3.1    | Initial Data Pass                 |   |

|   |     | 5.3.2    | Computational Algorithm Selection | 3 |

|   |     | 5.3.3    | Accumulation of Final Results     | 4 |

|   |     | 5.3.4    | Topology Selection                | 4 |

|   | 5.4 | Convo    | lution                            | 5 |

|   |     | 5 1 1    | Design of the Implementations 5   | 5 |

|   | 7 1       | mL:-   | · C                             | ۵n |

|---|-----------|--------|---------------------------------|----|

| 7 | Con       | clusio | <b>n</b> .                      | 90 |

|   | 6.4       | Remai  | rks                             | 88 |

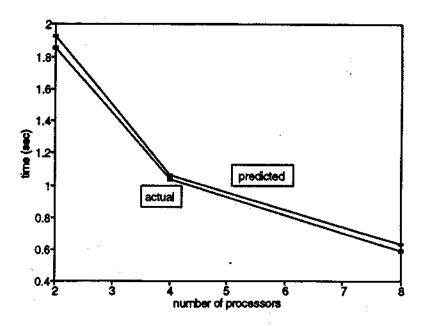

|   |           | 6.3.4  |                                 | 88 |

|   |           | 6.3.3  | Communication Time              | 87 |

|   |           | 6.3.2  | Computation Time                | 86 |

|   |           | 6.3.1  | Notation                        | 86 |

|   | 6.3       | Regula | ar Moment Model                 | 86 |

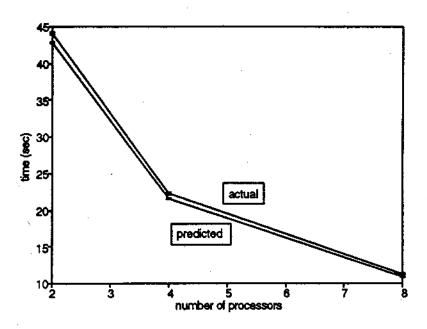

|   |           | 6.2.4  | Overall Time                    | 85 |

|   |           | 6.2.3  | Communication Time              | 83 |

|   |           | 6.2.2  | Computation Time                | 82 |

|   |           | 6.2.1  | Notation                        | 82 |

|   | 6.2       | Convo  | lution Model                    | 82 |

|   | 6.1       | Introd | uction                          | 81 |

| 6 | Per       | formar | nce Modelling                   | 81 |

|   | 5.7       | Remai  | rks                             | 80 |

|   | <b></b> - | 5.6.2  | Moments                         | 78 |

|   |           | 5.6.1  | Convolution                     | 77 |

|   | 5.6       | -      | sis of the Implementations      | 77 |

|   |           | 5.5.4  | Add and Multiply Implementation | 71 |

|   |           | 5.5.3  | Partial Sum Implementations     | 67 |

|   |           | 5.5.2  | Recursive Implementation        | 65 |

|   |           | 5.5.1  | Design of the Implementations   | 64 |

|   | 5.5       | Regula | ar Moments                      | 63 |

|   |           | 5.4.4  | Tree Implementation             | 60 |

|   |           | 5.4.3  | Ring Implementation             | 57 |

|   |           | 5.4.2  | Pipeline Implementations        | 56 |

| 7.2    | Future | Work . | • | <br>• | • | ٠ | ٠ | ٠ | • | • | ٠ | ٠ | • | • | • | • | • | • | • | ٠ | • | • | • | • | • | ٠ | ٠ | ٠ | • | • | • | 91 |

|--------|--------|--------|---|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| Refere | nces   |        |   |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 93 |

# List of Tables

| <b>4</b> .1 | Single Transputer Convolution Timing Results in Seconds    | 39 |

|-------------|------------------------------------------------------------|----|

| 4.2         | Single Transputer Regular Moment Timing Results in Seconds | 41 |

# List of Figures

| 2.1        | The B008 Motherboard                                                 | 14 |

|------------|----------------------------------------------------------------------|----|

| 2.2        | Optimal Transputer Programming Model                                 | 15 |

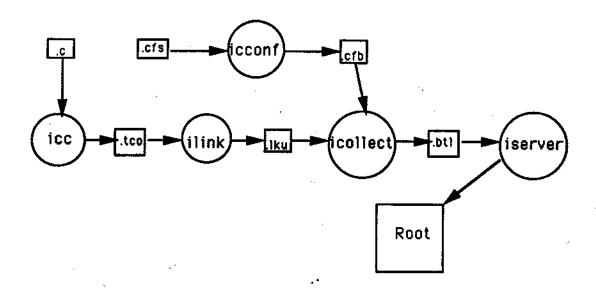

| 2.3        | Parallel C Compilation Process                                       | 19 |

| 3.1        | A Grey Level Image                                                   | 22 |

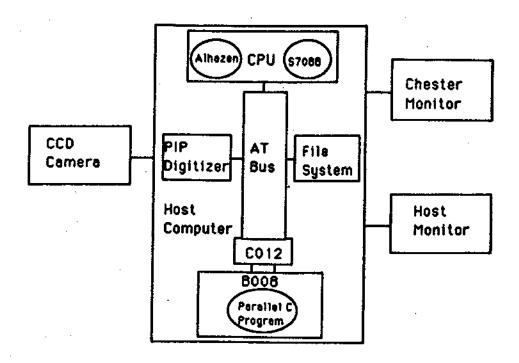

| 3.2        | Our Multi-Transputer Based Image Processing System                   | 24 |

| 3.3        | Convolution Algorithm                                                | 26 |

| 3.4        | Straightforward Algorithm for Moment Calculation                     | 29 |

| 3.5        | Coefficient Storage Algorithm for Moment Calculation                 | 30 |

| 3.6        | Column Product Storage Algorithm for Moment Calculation              | 31 |

| 3.7        | One Dimensional Add and Multiply Algorithm for Moment Calculation    | 32 |

| 3.8        | One Dimensional Recursive Algorithm for Moment Calculation           | 33 |

| 3.9        | One Dimensional Partial Sum Algorithm for Moment Calculation         | 35 |

| 4.1        | Convolution Timing Results for Various Mask Sizes                    | 40 |

| 4.2        | Convolution Timing Results for Various Image Sizes                   | 40 |

| 4.3        | Straightforward Algorithm Timing Results                             | 42 |

| 4.4        | Coefficient and Column Product Algorithm Timing Results              | 43 |

| 4.5        | Recursive, Partial Sum and Add and Multiply Algorithm Timing Results | 43 |

| 4.6        | Hybrid Algorithm Timing Results                                      | 44 |

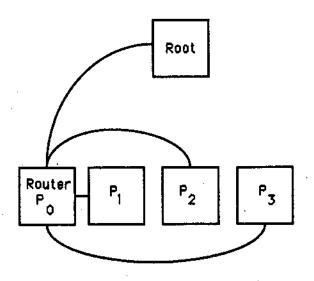

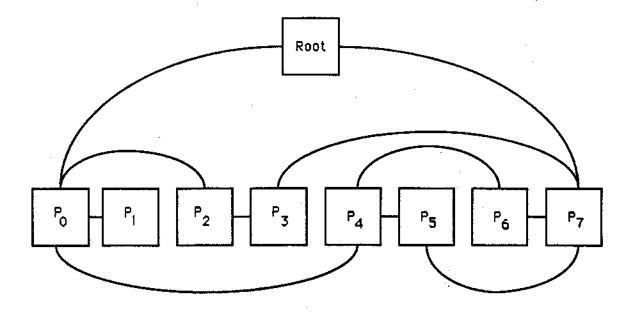

| 5.1        | Pipeline Subtopology                                                 | 51 |

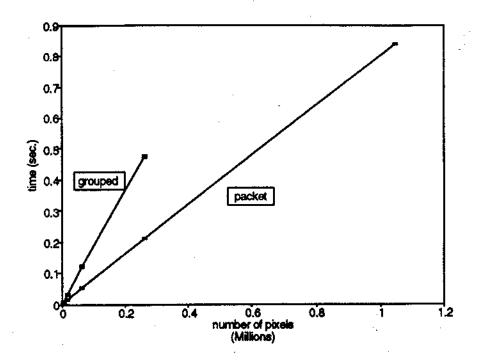

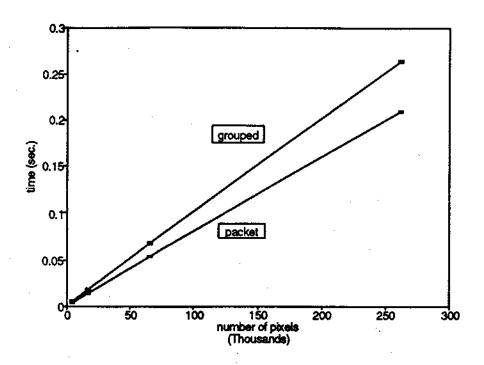

| <b>5.2</b> | Pipeline Data Passing Timing Results                                 | 52 |

| 5.3        | Tree Subtopology                                                     | 52 |

| 5.4  | Tree Data Passing Timing Results           |

|------|--------------------------------------------|

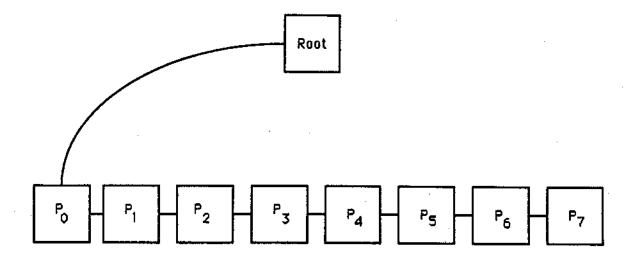

| 5.5  | Eight Transputer Pipeline Topology         |

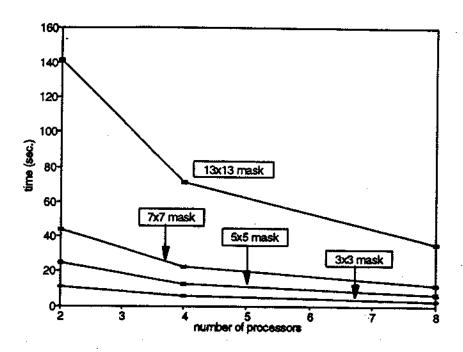

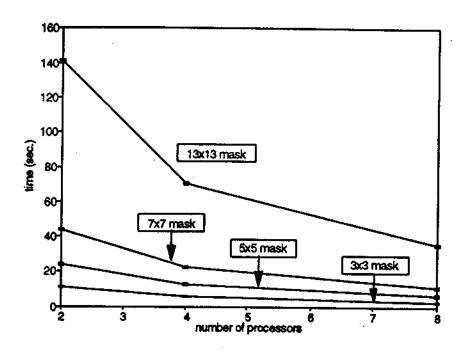

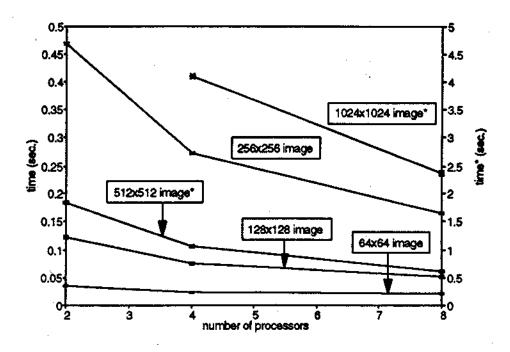

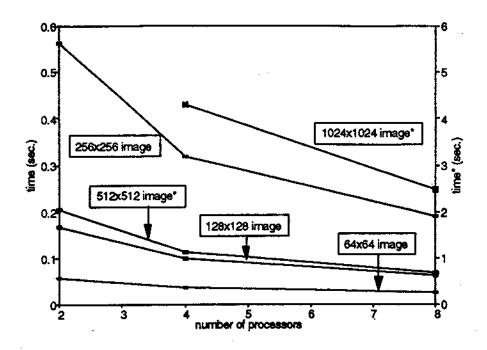

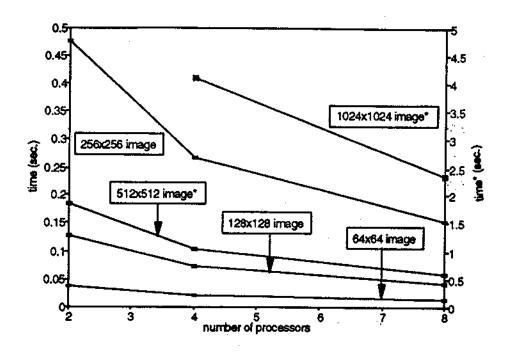

| 5.6  | Convolution Pipeline: Timing Results       |

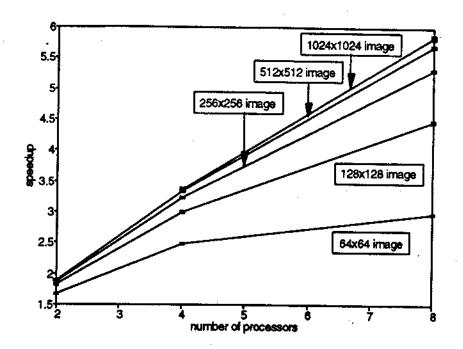

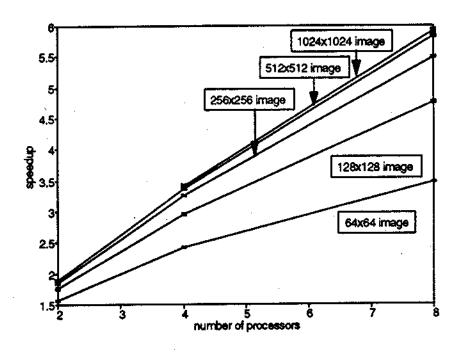

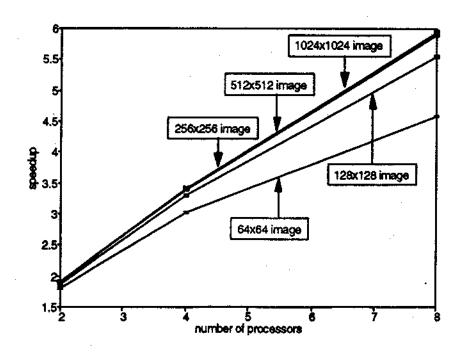

| 5.7  | Convolution Pipeline: Speedup Graphs       |

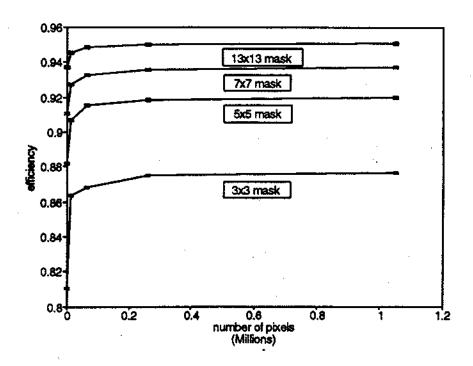

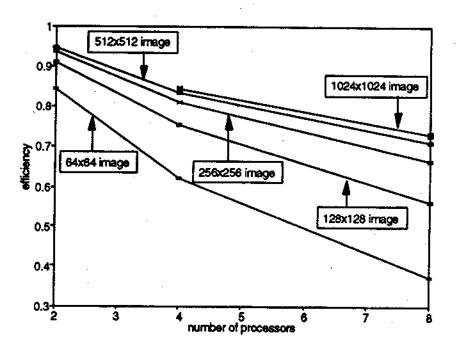

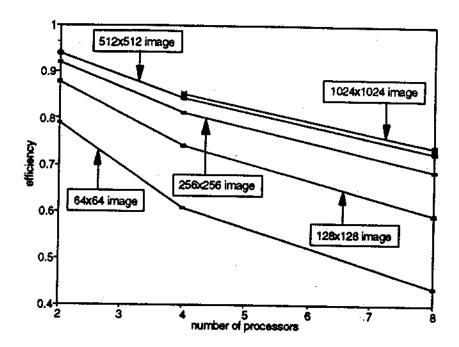

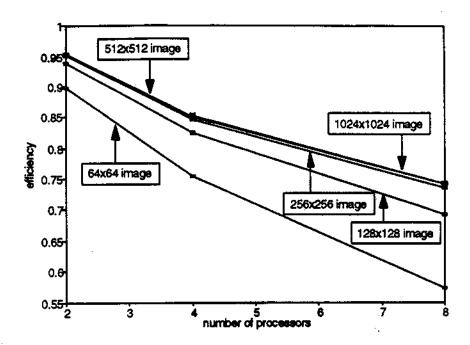

| 5.8  | Convolution Pipeline: Efficiency Graphs    |

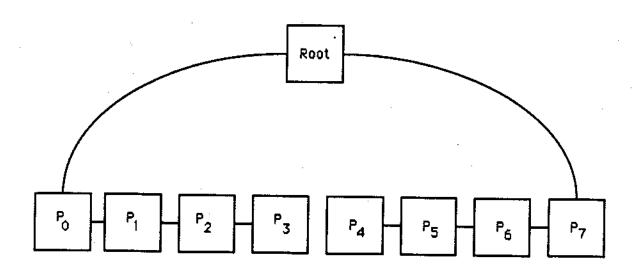

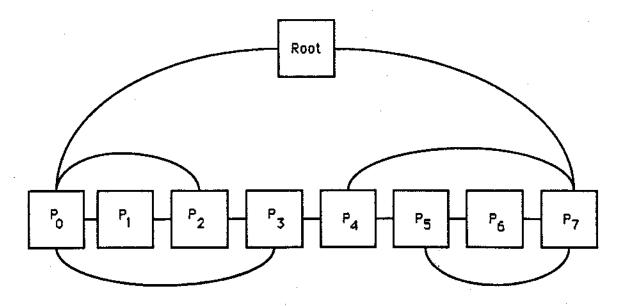

| 5.9  | Eight Transputer Ring Topology             |

| 5.10 | Convolution Ring: Pseudo Code              |

| 5.11 | Convolution Ring: Timing Results 61        |

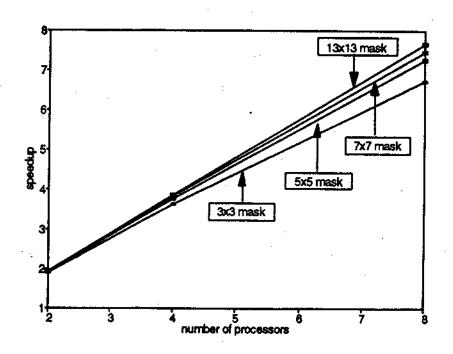

| 5.12 | Convolution Ring: Speedup Graphs 61        |

| 5.13 | Convolution Ring: Efficiency Graphs 62     |

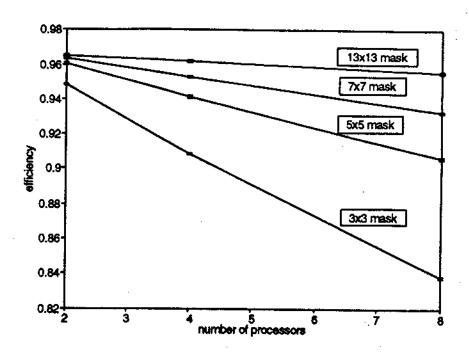

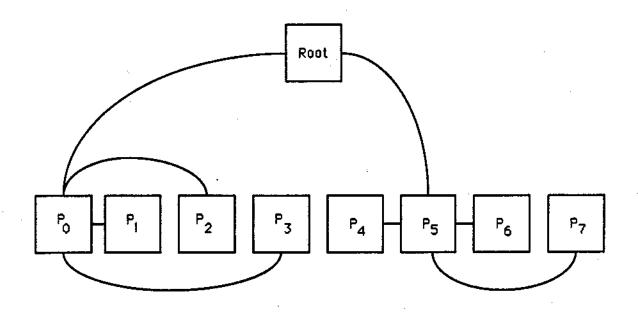

| 5.14 | Eight Transputer Tree Topology             |

| 5.15 | Convolution Tree: Efficiency Graphs 63     |

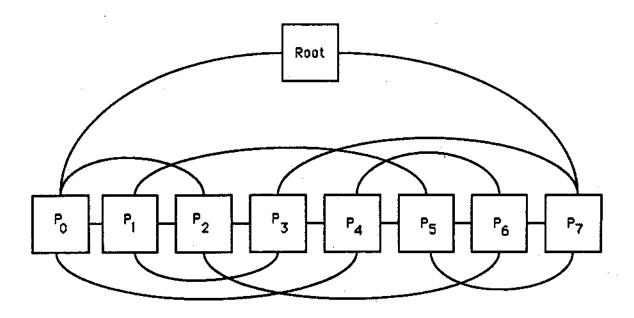

| 5.16 | Eight Transputer Recursive Topology        |

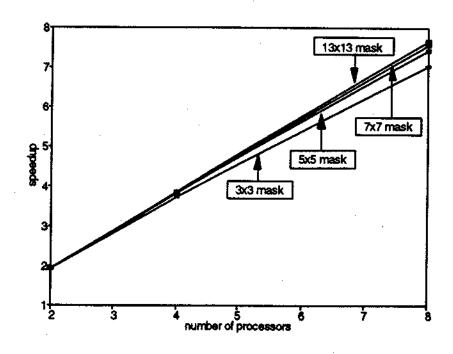

| 5.17 | Recursive Timing Results                   |

| 5.18 | Recursive Speedup Graphs                   |

| 5.19 | Recursive Efficiency Graphs                |

| 5.20 | Eight Transputer Partial Sum Topology      |

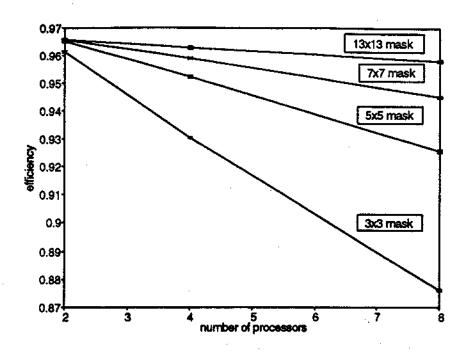

| 5.21 | Partial Sum Timing Results                 |

| 5.22 | Partial Sum Speedup Graphs                 |

| 5.23 | Partial Sum Efficiency Graphs              |

| 5.24 | Eight Transputer Add and Multiply Topology |

| 5.25 | Add and Multiply Pseudo Code               |

| 5.26 | Add and Multiply Timing Results            |

| 5.27 | Add and Multiply Speedup Graphs            |

| 5.28 | Add and Multiply Efficiency Graphs         |

| 6.1  | Convolution Model Graphs                   |

| 6.2  | Regular Moment Model Graphs                |

# Acknowledgements

I would like to thank my supervisors Professor V. C. Bhavsar and Professor P. Pochec. Partial financial support through the NSERC operating grants OGP00089 and OGP0105827 of Professor Bhavsar and Professor Pochec is also acknowledged. The U.N.B. supercomputing group deserves special thanks, especially Brian d'Auriol, the 'transputer pioneer' at U.N.B. Mr. d'Auriol's groundwork in the area during 1991 and willingness to answer my questions greatly hastened completion of this thesis.

I am grateful to U.N.B. students Eric Drummie and Derrick Weaver for putting me up during the early winter of 1991. I would also like to thank Fredericton soccer players Geoff Downey, Tom Hanley and Jean LeBlanc for their support and encouragement. Most importantly of all, I would like to thank my family, on whose strength I have drawn every day while in New Brunswick.

# Chapter 1

# Introduction

One of the great scientific challenges of the 1990's seems to be keeping pace with man's ever increasing appetite for computational power. It seems that as soon as new, faster computers become available, new applications are found that make them seem inadequate. In addition, in recent years it has become increasingly obvious that the era when orders of magnitude improvement in processor speed can be expected is coming to an end. The laws of physics dictate that there is a limit to how powerful traditional single processor computers can be. The only solution to the problem seems to be to use computers with more than one processor. This is known as parallel processing. While many advances have already been achieved in this area, it is clear that man has only begun to discover the potential of parallel computing.

The T800 transputer is a VLSI processor marketed by INMOS Ltd. Transputers can be used individually or linked together into reconfigurable networks. Applications can be programmed on these networks using special transputer programming languages such as Parallel C. These networks form relatively inexpensive and flexible parallel computers. Transputers are often mounted in boards which are connected to host computers. The B008 motherboard, also released by INMOS, can house up to ten T800 transputers.

One area of computer science that can benefit from the computational power

of parallel processing is image processing. Image processing deals with the transformation and analysis of pictures. Real-time image processing applications require operations to be executed on the thousands of pixels that make up image frames many times each second. One operation commonly performed in such applications is feature extraction. Feature extraction is the act of finding distinguishing features or measures in images. Features can be either local or global. Convolution, which involves the passing of a mask over an image is a local feature extraction process. Statistical regular moments, on the other hand, are global image features.

# 1.1 Thesis Objective

The feasibility of transputer based image processing systems has been discussed in [13, 19]. The objective of the thesis is to develop efficient parallel implementations of the image processing techniques of convolution and regular moments on a B008 motherboard containing nine T800 transputers programmed with Parallel C. Our main criterion for judging the efficiency of an implementation will be its execution time. Its memory requirements will also be considered. Special attention will be given to implementation performance as image size and number of processors increases.

We acknowledge that just as moments and convolution are only examples of image processing techniques, using the B008 and Parallel C is only one method of computing with transputers. Therefore, we would like to abstract from the special considerations of our chosen image processing techniques and transputer model and give some attention in our research to the more general issue of efficient image processing on transputers. Specifically, we would like to discover some principles and ideas that are applicable to any transputer based image processing application. Ideally, our research might lay the foundation for a generic efficient image processing system on message passing, distributed memory multiprocessor systems.

An alternative approach to the research is to use the reconfigurability of transputer networks to find the best implementations for regular moments and convolution on certain topologies commonly found in parallel computing (e.g., ring, mesh, binary tree). In this approach, transputers become an experimental model for image processing on parallel computers. We believe, however, that transputers are appropriate themselves for image processing and that the issues related to their use for image processing applications are sufficiently interesting and challenging to merit investigating image processing on transputers for its own sake.

# 1.2 Strategy

Multi-transputer programming is sufficiently complicated to challenge even the best programmer. A starting point is necessary from which parallel programs can be developed. Our approach is to begin by implementing more traditional, single process programs on a single transputer in Parallel C. Next we will program multi-process programs and run them on a single transputer. These programs will be finally converted to run on multiple transputers. When designing the multi-transputer programs, we intend to take into consideration the following issues: 1) topology selection; 2) data passing techniques; and 3) parallel computational algorithm selection.

## 1.3 Thesis Structure

The second chapter gives the reader a broad introduction to parallel processing. Emphasis is given to transputers and Parallel C. Chapter 3 introduces image processing, focusing on our transputer based image processing system and the techniques of regular moments and convolution. Chapter 4 gives timing results for our single transputer implementations. Chapter 5, the longest in the thesis, gives timing results for and analyzes our eight multi-transputer programs. Performance modelling for two of those

implementations is presented in Chapter 6. The thesis ends with a conclusion which summarizes our work and discusses some possible avenues for future research.

# Chapter 2

# Parallel Processing

#### 2.1 Introduction

The computational power of any traditional, single processor computer is largely determined by three factors: the speed of its CPU, the speed and extent of its main memory and the speed and size of the channel between its CPU and main memory. The last factor, the classic 'Von Neuman bottleneck' is the most restrictive to today's single processor computers [6]. Parallel computers, computers which incorporate parallel processing, circumvent at least one of the above restrictions. In this chapter we discuss parallel processing. It should be noted that parallel processing is an extremely diverse, complicated branch of computer science. A comprehensive examination of it would likely fill several volumes. Our approach in this chapter is to introduce the reader to its most important aspects, paying special attention to the ones needed to understand the research we later present. For more information about a given topic, the reader should consult the listed reference.

We begin the chapter with an examination of the various types of parallel architectures. Next, parallelization techniques of sequential algorithms are discussed. Some useful terms and definitions related to parallel processing are discussed in the following section. A section devoted to transputers follows these definitions. Parallel

C, the language we have used to program the transputers, is next described. Some concluding remarks close the chapter.

#### 2.2 Parallel Architectures

There is a bewildering number of different kinds of computers in the 1990's. Great differences exist in architecture and technology from one machine to another. While advances in computer technology seem to occur virtually every day, (consider, for example, recent breakthroughs in chip design and makeup) the architectures themselves have been relatively unchanged. In this section we attempt to describe the various architectures of current computers and give examples of machines that use them. There are four main factors to consider when classifying the architecture of a parallel computer. The first is how many data streams it has. The second is whether or not the computer's processors can execute different instructions at one time. The computer's memory type is also relevant. Lastly, how a parallel computer's processors communicate with each other must be considered when classifying it. We next describe each issue in more detail.

#### 2.2.1 Data Streams

The processors of a parallel machine can either access data through the same path or can have their own path to data. In the first case, the parallel machine is said to be a Single Data Stream machine. Those machines whose processors have their own path to data are called Multiple Data Stream computers.

#### 2.2.2 Instruction Streams

If a computer can execute only one instruction at once, it is referred to as a Single Instruction Stream machine. Obviously, all single processor sequential computers are single instruction stream machines. Some multiple processor machines contain many simple processors which all perform the same action at the same time (Single Instruction Stream Multiple Data Stream machines). Others have more sophisticated processors which can do different operations simultaneously. The latter are called Multiple Instruction Stream computers.

#### 2.2.3 Memory Type

Some parallel computers have a single memory which is accessed by all of its processors. These machines are said to be shared memory machines. On the other hand, the processors of some machines have their own memory space. They are called distributed memory machines. It is possible for both types of memory to be found in one parallel computer.

#### 2.2.4 Communication Method

If the processors of a parallel computer communicate and share data by means of a central shared memory, the computer is referred to as a tightly coupled machine. If, on the other hand, its processors communicate directly with each other through communication links, without a shared memory, the parallel machine is loosely coupled. In the former case, the processors must be carefully controlled so that memory contention is resolved and no processor can access data that another is altering. In the latter case, the computer's processors can run independently and asynchronously, but must have message passing capability for communication [25].

The above four factors can be combined to get many kinds of parallel machines. Conventional single processor, single memory computers are classified as Single Instruction, Single Data (SISD) machines. Most arrays of VLSI processors are Single Instruction, Multiple Data (SIMD) distributed memory computers. Vector supercomputers are also usually SIMD machines. Transputers, as we shall see, are loosely

coupled Multiple Instruction Stream Multiple Data Stream (MIMD) computers.

# 2.3 Parallelization Techniques

A parallelization technique is a method of doing a problem on a parallel computer. The three major ways of doing problems on parallel machines are data parallelism, instructional parallelism and processor farming. In this section, we discuss each.

#### 2.3.1 Data Parallelism

The conceptually simplest parallelization technique is data parallelism. In the data parallelism method, each of many processors executes the same instructions on part of a large amount of data. This is the technique used by vector supercomputers.

#### 2.3.2 Instructional Parallelism

In contrast with data parallelism, in instructional parallel programs the processors work together to perform a computation on the same data. The processors usually execute different operations on the data. The best example of instructional parallelism is pipeline processing. In this case, each processor in a line of processors performs a separate action on the data and then passes it to the next processor in the line.

## 2.3.3 Processor Farming

Another common approach is processor farming. In farming, a central supervisory 'farmer' processor dynamically allocates tasks for several 'worker' processors. The workers perform the tasks they are allocated and send the results back to the farmer. The process continues until all necessary work is done.

#### 2.4 Terms and Definitions

In this section, we present some of the terms and definitions associated with parallel processing.

#### 2.4.1 Speedup

The speedup of a parallel implementation with P processors is defined to be the time taken for the task on one processor divided by the time taken on the parallel implementation. The concept of speedup is formalized in Equation 2.1.

$$S(P) = T(1)/T(P)$$

(2.1)

A linear speedup for an implementation is preferred since it usually indicates that the implementation has overhead directly in proportion to the number of processors. However, in many practical implementations, the overhead usually increases more than linearly as the number of processors increases, resulting in speedup curves which flatten out as the number of processors increases.

# 2.4.2 Efficiency

The efficiency of a P processor parallel implementation is defined as the speedup of the implementation divided by P. Equation 2.2 expresses efficiency in formal terms.

$$E(P) = S(P)/P \tag{2.2}$$

The efficiency of an implementation can never exceed one. Implementations with efficiencies close to one are preferable. However, an inefficient implementation of one parallel algorithm may still be faster than an efficient implementation of a slower parallel algorithm. It is a measure of how well the implementation uses the hardware, and not how good the algorithm used by the implementation is.

#### 2.4.3 Parallel Processor Cost

For a P processor parallel implementation, this is defined as the product of the time taken for the task and P, the number of processors. This is stated symbolically in Equation 2.3.

$$C(P) = T(P) * P \tag{2.3}$$

This measures the unit cost of the parallel implementation.

## 2.4.4 Granularity

There are three types of granularity, problem granularity, task granularity and computer granularity.

#### **Problem Granularity**

The granularity of a problem refers to the size of the parts into which it may be subdivided for parallel processing. A problem is said to be *fine grained* if these parts are relatively small, *large grained* if they are large.

#### Task Granularity

The granularity of a task or process measures the amount of computation that can be performed without required communication/synchronization with other tasks.

#### Computer Granularity

Computer granularity measures the ratio of the number of processors on a parallel machine to their power. A large grained parallel machine has a few very powerful processors. Most supercomputers are large grained. On the other hand, a fine grained computer has numerous slower, simple processors. A VLSI chip with many processors is a good example of a fine grained parallel machine. Best results usually are achieved

when the granularity of the desired problem is close to the granularity of the machine upon which it is to be executed.

## 2.5 Transputers

In 1984 INMOS Ltd. of Great Britain began development of a VLSI processor based on a novel idea. Until then, most programming languages had been designed to run on a given computer architecture (usually SISD). INMOS's idea was to design its processor to implement an existing parallel programming language. The processor is called a transputer (an acronym for TRANSistorized comPUTER). The language is called OCCAM. OCCAM and its successor OCCAM 2 implement the Communicating Sequential Process model of parallel computation.

### 2.5.1 Communicating Sequential Processes

Communicating Sequential Processes (CSP's), were proposed in 1978 by Hoare [11]. A CSP is one of at least two simultaneously executing processes which communicate and synchronize themselves by means of message passing through channels. The processes successively perform an operation on data and pass the altered data on to the next process through the channel connecting them.

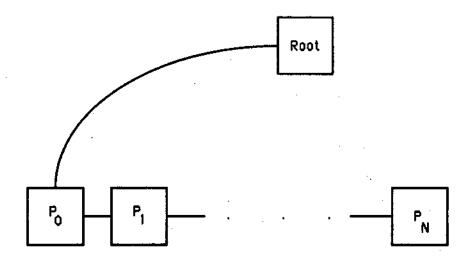

### 2.5.2 Transputer Networks

It is possible to use transputers by themselves, but they are computationally most effective when many are connected together into a network. In the latter case, the transputers are usually placed in a board such as the IMS B008 (see Section 2.5.7) that is connected to a host computer. A special transputer called the root is connected to the host and can access its monitor, disk drive and keyboard. Transputer networks

form loosely coupled parallel machines implementing the MIMD distributed memory parallel architecture. This makes them ideal for implementing both data parallel and instructional parallel algorithms. Since most such networks contain relatively few transputers (usually less than 128), and since each transputer is quite powerful computationally, they are considered to be relatively large grained machines. The networks are created by connecting pairs of the high speed bidirection links on each transputer together. These links are used for data communication and synchronization between the two connected transputers. Many different network topologies can be formed in this way. Once created, these networks can be programmed using OCCAM2 or another transputer programming language such as Parallel C. Special operating systems (e.g. HELIOS) are available that are designed for transputer environments [21].

#### 2.5.3 The IMS T800 Transputer

Released in October 1988, the T800 is a powerful transputer currently available from INMOS. It has up to 4 Megabytes of RAM and a clock rate of 30MHz. The T800 has a 32 bit CPU and a 64 bit floating point unit. Its four bidirectional links send data at a rate of 2.35 Mbytes per second. Its peak performance is rated at 2.25 MFLOPS for a 30MHz clock rate. Graphics support is available.

#### 2.5.4 The IMS C012 Communication Device

The C012 performs parallel to serial and serial to parallel conversions back and forth from the main host bus to the root transputer on the B008. The IMS S708B device driver is a program on the host which assists in this data transfer.

#### 2.5.5 The IMS C004 Link Switch

The C004 is a crossbar switch used to reconfigure the B008 motherboard. It has 32 link ports which can be connected together for this purpose.

### 2.5.6 The IMS T222 Network Configuration Transputer

This 16 bit transputer is responsible for resetting the C004 crossbar switch in order to change the topology of the B008.

#### 2.5.7 The IMS B008 Motherboard

The B008 has ten slots for TRAMS or TRAnsputer ModuleS. The first slot contains the root transputer. Each slot has four link connections which are joined to the links of the transputer placed in the slot. The ten slots are permanently connected into a pipeline using two of the links of each slot. The other two links are connected to a C004 crossbar switch. The notable exception is the first slot. Its first link is connected to a C012 communication device. The second link is connected to a T222 network configurer. Its third link is connected to the second slot. The fourth and final link is connected to the C004. Figure 2.1 shows the B008 configuration.

During network reconfiguration, the C004 gets the information about how to connect its links from a network configuration program which executes on the T222. The program receives two host files containing Module Motherboard Software (MMS) code. The first file describes the B008 hardware and its hardwire (permanent) connections. The second lists the softwire (temporary) link connection information needed for the new topology. Using this information, the program sends the C004 the low level linking commands necessary to complete the topology and reset the B008. Network configuration is done by executing the *tnconfig* command on the two MMS files. This causes the *iserver* to send the information in the files to the T222.

## 2.5.8 The IMS T9000 Transputer

The eagerly awaited T9000 transputer is the centrepiece of the next generation of transputer technology currently in development at INMOS. It features an order of magnitude improvement in link and processor speeds. Its most interesting new aspect

Figure 2.1: The B008 Motherboard

though, is its virtual channel processing capability. This will automate the routing of data packets. Previously the programmer had to perform this in software. Latest estimates indicate that the technology will be available in the summer of 1993.

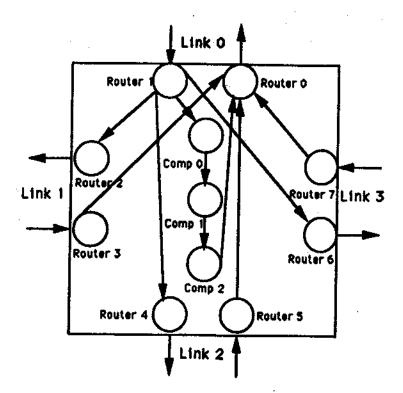

# 2.5.9 Optimal Transputer Programming Model

In order to exploit the full potential of the multi-transputer parallel model, the following method can be used to program each transputer. One asynchronous routing process is dedicated to control each unidirectional transputer link. In addition, one or more asynchronous processes are created to perform all computation on the transputer. The routing processes control data flow to and from the transputer and to and from the computational processes. The computational processes are analogous to procedures in a conventional single processor program. They act as Communicating Sequential Processes. Each one performs a separate computational task, then passes the resulting data to the next computational process or to a routing process and then terminates. Data communication and synchronization among all the processes is achieved by means of soft channels. These unidirectional channels between processes are analogous to the hard transputer link channels which connect transputers. Just as any two transputers which must communicate must be connected by a link, so too must any two processes which communicate be connected by a soft channel. Routing processes may be connected to each other or to computational processes. Obviously, the computational processes must also be connected by a channel. Figure 2.2 gives a schematic diagram for this method of programming a transputer. The use of this programming method not only enables parallel transputer implementations to run as fast as possible but also makes it easier to avoid deadlock in data passing operations between transputers.

Figure 2.2: Optimal Transputer Programming Model

### 2.6 Parallel ANSI C

Just as OCCAM 2 evolved from OCCAM, Parallel ANSI C evolved from an earlier language developed by 3L Ltd. It is a superset of ANSI standard C, which in turn standardized and improved upon Kernighan and Ritchie's C. Its additional features allow for parallel processing on transputers using the CSP model. Parallel ANSI C programs consist of one or more source files and an optional configuration source file. These are described below.

#### 2.6.1 Source Files

Parallel ANSI C source files are quite similar to ANSI C source files. They have the c file extension usual for C programs. In addition, each must include a main() function returning an int. The similarities end there, however. During compilation, each source file is either linked with the full or the reduced library of functions to produce a linked unit process binary. (See Section 2.6.3 for a description of the compilation procedure.) There must be one linked unit connected to the host in each Parallel C program. Linked units connected to the host must be linked with the full library. They may access the command line parameters argv and argc. Such units may also use the entire io library including such functions as printf and fgetc. Other linked units cannot use these functions.

Within each source file, local synchronous and asynchronous processes can be created and run at high or low priority. Parallel C allows for the creation of local 'soft' channels for communication and synchronization between these local processes as in the CSP model. The get\_param() function can be used to map a soft channel onto a connection between two linked units defined in the interface statement in the configuration source file of the implementation as described in Section 2.6.2. In the case of programs consisting of more than one linked unit (or, equivalently, more than one source file) the units can be connected for data communication. The units may

also be configured to run on a network of transputers. The last two operations are accomplished by means of configuration source files.

#### 2.6.2 Configuration Source Files

Each multi-transputer implementation requires a configuration source file. These files, which have the extension cfs, can be compiled and used with the linked unit process binaries to produce an executable file for the entire implementation. Each configuration source file contains C-like code that describes both the implementation's hardware (transputer) and software (linked unit process) configurations and the mapping between them. First of all, a description of the current transputer topology is given. This includes the types of all the transputers used and the links that are connected between them. Next, all the linked unit processes in the implementation and their parameters are given. The parameters are listed in a special interface statement after the name of the linked unit. Input and output channels can be among these parameters. These roughly correspond to transputer links and can be connected together in the configuration source file. The memory requirements of each linked unit must also be given. Optionally, a memory ordering and the execution priority of the unit can be added. Lastly, a process-to-processor mapping description is given. This simply states which linked units run on which transputers. In the general case, L linked unit processes can be placed on P transputers. The only restriction is that two connected processes cannot be placed on different transputers if there is no available connected link between the transputers for the processes to use for communication.

### 2.6.3 Program Compilation and Execution Processes

The compilation process for Parallel C programs is quite complicated. The following is a simplified version of what occurs. First of all, each source (c) file must be compiled using the icc command. The resulting transputer object code files are given

the extension tco. Next, the linker program ilink resolves all external references in these object files. It links the object files with the necessary libraries and produces a single linked unit for each with extension lku. In the case of multi-transputer programs, the network configurer icconf then compiles the configuration source file of the implementation into a binary configuration data file having extension cfb. In the last stage of compilation the implementation code is collected into a single bootable binary file with extension btl. This is the job of iccollect, the code collector. For single transputer programs, iccollect generates a bootable file by simply adding bootstrap code to the single linked unit. However, in the case of multi-transputer programs, the collector uses the information in the configuration data file to combine all linked units into a bootable. In either case, the bootable contains all transputer executable code and information for passing it to the transputers in the network. The iserver writes the bootable file to the boot link of the root transputer and execution begins. In Figure 2.3 there is a flow chart diagram of the compilation and execution processes.

#### 2.7 Remarks

When complemented with a toolkit supplied by INMOS, the B008 containing T800 transputers programmed with Parallel C forms a complete parallel programming environment. Its greatest advantage is its flexibility. Its MIMD architecture dictates that both data parallel and instructional parallel algorithms can be implemented. Another positive characteristic is its relative inexpensiveness. Its major disadvantage, on the other hand, is that a great deal of training and background knowledge is required to learn how to use it properly. Multi-transputer programming is a challenging, complicated exercise even to an experienced sequential programmer. Once mastered, however, it can be used to efficiently program a wide variety of applications.

Figure 2.3: Parallel C Compilation Process

# Chapter 3

# Image Processing

#### 3.1 Introduction

In this chapter we introduce image processing, concentrating as in Chapter 2 on the areas needed to understand this thesis. Image processing has been undertaken for nearly three quarters of a century. Computers were not used extensively for the task before the 1960's despite the fact that their ability to execute instructions quickly on a large amount of data made them well suited to it [9]. Image processing encompasses areas such as image enhancement and pattern recognition. Image enhancement involves the improvement of the quality of images for human observation. Its techniques include histogram equalization, crispening and smoothing. Pattern recognition, on the other hand, attempts to place visual patterns into one of many possible classes. To do so, distinguishing features or measures are first extracted from each pattern. These features are used to determine which class the pattern best fits. The features can be either local or global. Our work focuses on the two feature extraction techniques of convolution and statistical moments.

The chapter proceeds as follows. First we describe how images are represented in computers. Image processing equipment is discussed in the next section. A section about image processing systems comes next. We devote one section to each of the

two feature extraction techniques implemented in our work, convolution and regular moment extraction. Some remarks about the algorithms used in our work conclude the chapter.

# 3.2 Digital Representation of Images

Images must be converted to digital form for storage and processing on computers. This digitization occurs in two ways, spatially and in brightness. First, images must be sampled at a finite number of points in space. Usually, this sampling is done on square  $N \times N$  grids where N is equivalent to a power of 2. Each sampled point is referred to as an image pixel. The pixels are assigned a discrete intensity value called a grey level which approximates the image brightness at that point. These values are usually non-negative integers that range from 0 to I-1 with I again usually being equal to a power of 2. The resolution of a digital image refers to the number of pixels it has. The greater the number of pixels, the higher the resolution will be.

The resulting digital representation of the image is referred to as a grey level image. Clearly, the greater the values of N and I, the more accurate the grey level image will be. However, as N and I increase, the number of bits required to store the image increases as  $N^2 \log_2 I$ . In particular, the storage requirements for a  $1024 \times 1024$  image with 256 grey levels would be  $1024 \times 1024 \times 8$  bits or 1 Megabyte. This is acceptable for storage on disk, but might be impossible for main memory storage in smaller computers. More importantly, the processing time needed for most image processing techniques increases quadratically with the image size N. This may entail that the system response time is too slow on some computers for large images. It is also important to note that images with a relatively narrow dynamic range in intensity values may not require a large dynamic range of grey levels. Figure 3.1 shows a  $256 \times 256$  grey level image with 256 original grey levels. (The printed image has been enlarged and may contain fewer grey levels.)

Figure 3.1: A Grey Level Image

# 3.3 Image Processing Equipment

#### 3.3.1 Cameras

Cameras convert the visual scene before them into an analogue TV signal such as the RS-170. They use a two dimensional array of sensors which measure the brightness of each part of the scene to produce frames of analogue voltage pulses. The frames are stored in the camera's frame grabber. They are updated at least thirty times a second. The information in the frames is modulated onto an analogue television signal which is the output of the camera. Cameras that directly produce digital grey level images also exist. (See for example [22].) While usually quite expensive, they serve to eliminate the need for the analogue to digital conversion of video signals usually performed by digitizers.

#### 3.3.2 Digitizers

Digitizers convert the analogue voltage signals of image frames produced by most cameras to grey level intensity values. Quantization errors (the difference between the grey level and the actual brightness) usually occur in the process.

#### 3.3.3 Monitors

Monitors are used to display video images. They take an analogue video signal and output it to a raster screen.

# 3.4 Image Processing Systems

#### 3.4.1 Need for Parallel Processing

Cameras usually produce at least thirty frames every second. Each frame in turn consists of thousands or even hundreds of thousands of pixels. Most image processing techniques require operations to be performed on each of the pixels. For this reason, real-time image processing is too computationally intensive for a standard, single processor computer. The use of parallel processing seems to be the only way to achieve real-time image processing.

## 3.4.2 Our Multi-Transputer Based System

An IBM PS/2 Model 30 286 is the host computer for our image processing system. A CCD (Charge Coupled Device) camera is used to acquire images. It is connected to the MATROX PIP 1024 video digitizer board [20, 15] located in the host. The PIP is used to instantaneously store a frame from the camera in digital form. The B008 motherboard is also inside the host. It is connected to the host's 16 bit AT bus by way of the C012 communication device. The host file system is used to store images.

A CHESTER monitor (not to be confused with the host monitor) also connects with the host and is used to display images.

The ALHAZEN Image Acquisition System, a program running on the host, gets images from the digitizer and writes them to the host file system. Parallel C programs executing on the B008 acquire these images from the resulting binary, 8-bit ASCII files stored on the host. The programs then perform an image processing task on the images and output the result to files on the host. ALHAZEN can also be used to display images on the monitor, both those stored in the PIP digitizer and those in files on the host. The S708B device driver runs on the host. It controls the transfer of data from the host to the root transputer of the B008. Our multi-transputer based image processing system is shown in Figure 3.2.

Figure 3.2: Our Multi-Transputer Based Image Processing System

## 3.5 Convolution

Convolution has been extensively used in many areas of image processing. It involves the passing of a mask or filter over the image. The features enhanced by convolution are local ones. This means that they exist independent of the rest of the image. Different types of masks can be used to extract different kinds of features. Some image features extractable using convolution are lines, edges and points. Two commonly used masks are the Laplacian and the Sobel. The convolution of two discrete two dimensional functions f and g is defined to be

$$f_e(x,y) * g_e(x,y) = \sum_{m=0}^{M-1} \sum_{n=0}^{N-1} f_e(m,n) g_e(x-m,y-n)$$

(3.1)

for x = 0..M - 1 and y = 0..N - 1, where  $f_e$  and  $g_e$  are extended versions of the functions f and g, with additional zeros added outside the domain of the functions so that the convolution operation can be performed.

The reader can verify by examining Equation 3.1 that convolution requires many multiplications and additions to be performed. For real-time applications, the procedure may be computationally too intensive for a normal single processor computer. One approach [3] involves using the Fast Fourier Transform (FFT) to compute the Fourier transforms of  $f_e$  and  $g_e$ , multiplying the transformed functions and taking the inverse transform of the result to get the convolved function. Our approach to the problem is to spread the computation required over many processors.

## 3.5.1 Algorithm

The convolution algorithm involves many multiplications and additions. It is shown in Figure 3.3. F is a two dimensional  $N_1 \times N_2$  matrix storing the intensity function of the image. G is an  $M \times M$  matrix storing the function of the mask. C is the two dimensional  $N_1 \times N_2$  array storing the values of the convolved image function. It is assumed that floor M/2 zero pixels have been added around the edge of F.

```

CONVOL(F, N_1, N_2, G, M, C)

for i = 0..N_1 - 1

for j = 0..N_2 - 1

C(i, j) = 0

for k = 0..M - 1

for l = 0..M - 1

C(i, j) + F(i + k, j + l)G(k, l)

end for

end for

end for

C(i, j) = C(i, j) + C(i, j)

```

Figure 3.3: Convolution Algorithm

## 3.6 Moments

Statistical moments have also been widely used in image analysis. They are among the most significant of global image features. Many important geometric attributes of an image can be determined from its moments. Among these are its mass, spread and centre of inertia. Papoulis' uniqueness theorem [18] has established that no two images can have the same set of moments. This property ensures that moments are effective as a means of distinguishing among patterns. In addition, object features called moment invariants, which do not change if a geometric operation (as defined in Section 3.6.1) is performed on the object, can be derived from moments. Moments are therefore a valuable tool for image analysis. The formula for calculating  $m_{KL}$ , the (K, L)th regular moment of a discrete two dimensional function f(i, j), i = 1...N, j = 1...N is

$$m_{KL} = \sum_{i=1}^{N} \sum_{j=1}^{N} i^{K} j^{L} f(i,j)$$

(3.2)

Central moments have also been frequently used in image processing. They can be derived from the regular moments of an image or can be calculated directly using the formula

$$\mu_{KL} = \sum_{i=1}^{N} \sum_{j=1}^{N} (i - \overline{x})^{K} (j - \overline{y})^{L} f(i, j)$$

(3.3)

with

$$\overline{x}=rac{m_{10}}{m_{00}}, \qquad \overline{y}=rac{m_{01}}{m_{00}}.$$

From Equation 3.2 it can be seen that moment calculation also requires a large number of multiplications and additions. This entails that it is a slow process on most sequential computers. There are at least two approaches to resolving this dilemma. The first is to treat the image as a representation of a single object and to calculate the moments of its boundary. Research indicates that much of the information encoded in an object's moments originates in the boundary areas of the object. It is therefore legitimate to calculate moment information only about the object boundary. Calculation of the moments of an object boundary is usually less computationally intensive than calculation of an image's overall moments. Images are treated as binary digital representations of a single object. The object's boundary is determined. To calculate the moments of the boundary, a special mathematical or geometrical technique is usually used. For example, Leu [16] first splits the object into triangles. The moments of the triangles are then calculated. The overall object moments are then calculated using the triangle moments. Another method is used by Li and Shen [14]. They propose using Green's theorem to calculate the moments along the boundary of the object. The other approach to moment calculation is to find clever parallel algorithms to calculate the overall image moments on many processors. This is our approach in this thesis.

## 3.6.1 Moment Invariants

An object feature is said to be invariant if it does not change when the object undergoes at least one of the geometric operations of scaling, rotation, reflection or translation. In 1961, Hu [12] proposed a set of invariant features based on moments. He derived six moment invariants using algebraic invariants from regular moments. They have been used in experiments to recognize planes [8] and ships [5]. In general, moment invariants are derivable from the regular moments of an image. In addition to their computational intensity, they have the drawback of being relatively noise sensitive. Many other moment invariants have been suggested besides Hu's. They have varying degrees of discrimination ability and noise sensitivity. Among these are Zernike moment invariants [24] and Bahmieh moment invariants [1]. For more information about moment invariants, the reader should consult the comparative study presented by Belkasim, Shridhar and Ahmadi [2].

## 3.6.2 Algorithms

There are eight algorithms for regular moment calculation used in our work. The most obvious way to calculate moments is the straightforward algorithm [7]. Figure 3.4 shows this algorithm for calculating the first 16 moments. In the moment algorithms, F is again the  $N_1 \times N_2$  matrix containing the image intensity function. m is the  $4 \times 4$  matrix containing the image moments.

Because  $2N^2$  exponentiations are needed to compute each moment, this algorithm is quite inefficient. An algorithm that avoids these calculations should be better. Notice that the column coefficient monomials  $j^i$  can be calculated using  $j^{i-1}$ . In particular,

$$j^{l} = jj^{l-1}. (3.4)$$

Reeves' coefficient storage algorithm [23] exploits this fact. The idea here is to create four  $N_1 \times N_2$  arrays C(l), l = 0..3 of column coefficient monomials using equation 3.4. These are then used to calculate the moments. Figure 3.5 shows the coefficient storage algorithm for the calculation of an image's first 16 regular moments.

```

STRAIGHT(F, N_1, N_2, m)

for k = 0..3

for l = 0..3

m_{kl} = 0

for i = 0..N_1 - 1

for j = 0..N_2 - 1

m_{kl} + = (i+1)^k (j+1)^l F(i,j)

end for

end for

end for

end for

```

Figure 3.4: Straightforward Algorithm for Moment Calculation

One drawback of the coefficient storage algorithm is that the products of image elements F(i,j),  $i=0..N_1-1$ ,  $j=0..N_2-1$  and coefficients are repeatedly calculated in the final stage of the algorithm. We can solve this problem by incorporating the image values in the four coefficient arrays. We call the resulting algorithm column product storage. The column product storage algorithm is shown in Figure 3.6.

There are two main problems with the storage algorithms. First, to process an  $N \times N$  image, the storage arrays require  $8N^2$  bytes, a great deal of memory for large values of N. In addition,  $O(N^2)$  multiplications would be needed to execute the algorithms on such an image. Multiplications are relatively computationally expensive for small VLSI processors.

The double summation in Equation 3.2 can be split into two separate summations. Equation 3.5 gives the resulting equation for the calculation of  $m_{KL}$ .

$$m_{KL} = \sum_{i=1}^{N} i^{K} \sum_{j=1}^{N} j^{L} f(i,j) = \sum_{i=1}^{N} i^{K} R M_{Li}$$

(3.5)

where

$$RM_{Li} = \sum_{i=1}^{N} j^L f(i,j)$$

```

COE(F, N_1, N_2, m)

\mathtt{for}\;i=0..N_1-1

for j=0..N_2-1

C(0,i,j)=1

end for

for l=1..3

\mathtt{for}\; j = 0..N_2 - 1

C(l,i,j) = (j+1)C(l-1,i,j)

end for

end for

end for

for l = 0..3

for k=0..3

m_{kl}=0

\mathtt{for}\; i=0..N_1-1

for j = 0..N_2 - 1

m_{kl}+=C(l,i,j)F(i,j)

C(l,i,j)*=i+1

end for

end for

end for

end for

END

```

Figure 3.5: Coefficient Storage Algorithm for Moment Calculation

```

COL(F, N_1, N_2, m)

\mathtt{for}\; i=0..N_1-1

for j = 0..N_2 - 1

C(0,i,j) = F(i,j)

end for

for l=1..3

for j=0..N_2-1

C(l,i,j) = (j+1)C(l-1,i,j)

end for

end for

for l=0..3

for k=0..3

m_{kl}=0

for i = 0..N_1 - 1

for j = 0..N_2 - 1

m_{kl}+=C(l,i,j)

C(l,i,j)*=i+1

end for

end for

end for

end for

END

```

Figure 3.6: Column Product Storage Algorithm for Moment Calculation

The calculation of the (K, L)th moment is thus split into two steps. First, the Lth one dimensional moment  $RM_{Li}$  of each image row is calculated. These row moments are then used to calculate the (K, L)th overall two dimensional moment  $m_{KL}$ . This is not unlike using the one dimensional Fourier transform to calculate the transform of a two dimensional function. The next three algorithms all use this technique to solve the problems associated with the storage algorithms.

We have created an algorithm similar to the storage algorithms that uses the above two step moment calculation technique. We have called it the add and multiply algorithm because addition and multiplication alternate in the process of moment calculation. Figure 3.7 shows the one dimensional add and multiply algorithm for the calculation of the first four row moments of a two dimensional discrete  $N_1 \times N_2$  function F. The moments are stored in M.

```

1DADDANDMU(F, N_1, N_2, offset, M) for i = 0..N_1 - 1 for l = 0..3 M(l, i) = 0 for j = 0..N_2 - 1 M(l, i) + = F(i, j) F(i, j) * = (j + offset + 1) end for end for end for END

```

Figure 3.7: One Dimensional Add and Multiply Algorithm for Moment Calculation

The two dimensional add and multiply algorithm for the calculation of the first sixteen overall image moments of an  $N_1 \times N_2$  image with intensity function F is equivalent to

```

1DADDANDMU(F, N_1, N_2, 0, RM); 1DADDANDMU(RM, 4, N_1, 0, m)

```

Although it has relatively small memory requirements, this algorithm still requires

$N^2 + N$  multiplications to calculate each moment of an  $N \times N$  image. It would be preferable that an algorithm use only additions to calculate moments. Budrikis and Hatamian have proposed an algorithm for regular moment calculation that does so [4, 10]. The algorithm uses recurrences to build up higher order moments from lower ones. To calculate the first 16 moments of an  $N \times N$  image, it only requires  $8N^2 + 32N$  additions. Figure 3.8 gives the pseudo code for this recursive algorithm. Again the first four one dimensional moments of the rows of a two dimensional  $N_1 \times N_2$  image function F are calculated and stored in M.

```

1DRECURSE(F, N_1, N_2, M)

for i=0..N_1-1

M0 = M1 = M2 = M3 = 0

PREVM1 = PREVM2 = 0

for j=0..N_2-1

M0+=F(i,N_2-1-j)

M1+=M0

M2+=M1+PREVM1

M3+ = M2 + M2 + PREVM2 - M1

PREVM1 = M1

PREVM2 = M2

end for

M(0,i)=M0

M(1,i)=M1

M(2,i)=M2

M(3,i)=M3

end for

END

```

Figure 3.8: One Dimensional Recursive Algorithm for Moment Calculation

As is the case with the two dimensional add and multiply algorithm, the two dimensional recursive algorithm is equivalent to

```

1DRECURSE(F, N_1, N_2, RM); 1DRECURSE(RM, 4, N_1, m)

```

Chen [7] has proposed another regular moment extraction algorithm that uses

only additions. He calls it the partial sum algorithm. The algorithm also uses lower order moments to calculate higher order ones. The technique employed here is to build up higher order moments by repeatedly partially summing over lower order moments. To calculate each row moment, each pixel is added to the pixel before it. Next each pixel is added to the pixel two before it. This process continues with the distance between added pixels doubling at each iteration until the distance is equal to half the image width. In this way,  $O(N^2 \log_2 N)$  additions are required to calculate each set of row moments of an  $N \times N$  image except the last. They may be calculated by simply summing the previous values of the intensity function F. As with the previous two algorithms, overall moments can be calculated using two applications of this technique. The partial sum algorithm for the calculation of the first four row moments of a two dimensional  $N_1 \times N_2$  function F is given in Figure 3.9.

In addition to the two dimensional add and multiply, recursive and partial sum overall moment extraction algorithms, six additional two dimensional algorithms can be created. To do so, the one dimensional algorithms are combined in pairs with one algorithm calculating the row moments and the other calculating the overall moments. Only two of these hybrid algorithms will be used in our research. Both use the recursive algorithm to calculate the row moments. The first uses the add and multiply algorithm to calculate the overall moments. The other uses the partial sum algorithm to do so. The first will be referred to as the recursive/add and multiply hybrid, the other as the recursive/partial sum hybrid.

# 3.7 Remarks

The convolution algorithm requires  $M^2N^2$  floating point multiplications and additions. Especially for large mask sizes M, we anticipate that it will have a slow single transputer implementation. We also intend to implement the straightforward, coefficient storage, column product storage algorithms and the two dimensional add and

```

1DPARSUM(F, N_1, N_2, M)

n = \log_2 N_2

for i = 0..N_1 - 1

for l=0..2

for index = 0..n - 1

offset = 2^{index}

for j = 0..N_2 - 1 - offset

F(i,j)+=F(i,j+offset)

end for

end for

if l \neq 2 then

M(l,i) = F(i,0)

end if

end for

firstOrderMomentSum = F(i, 0)

for j=0..N_2-2

F(i,j)+=F(i,j+1)

end for

M(2,i) = F(i,0)

for j = 1..N_2 - 1

F(i,0)+=F(i,j)

end for

M(3,i) = 3F(i,0) + M(2,i) - firstOrderMomentSum

end for

END

```

Figure 3.9: One Dimensional Partial Sum Algorithm for Moment Calculation

multiply, recursive, and partial sum algorithms on a single transputer. Of these six algorithms, only the recursive, partial sum, and add and multiply algorithms seem to hold much promise. The straightforward algorithm requires too many exponentiations to be efficient. The memory requirements of the two storage algorithms are prohibitive. Two hybrid algorithms will also be implemented for analysis purposes, as has been stated.

# Chapter 4

# Single Transputer Implementations

# 4.1 Introduction

Due to the large number of single processor algorithms used in our work, the single transputer implementations are quite extensive. In particular, nine of the thirteen single process algorithms mentioned in Chapter 3 have been implemented on a single transputer using Parallel C. Our goals in doing so are as follows: 1) to gain familiarity with developing programs in Parallel C on transputers, including, among other things, learning about the compilation process, creating makefiles and configuring source programs to run on transputers; 2) in the case of regular moments, to find the fastest algorithms for parallelization; 3) to create base code from which we could develop the multi-transputer implementations later; and 4) to develop straightforward correct implementations in order to assure ourselves that those more complicated multi-transputer implementations are correct.

In this chapter, we first describe the technique we have used to program the single transputer. A section devoted to the single transputer convolution implementation comes next. Timing results and analysis for the eight regular moment programs are

presented next. Some remarks conclude the chapter.

# 4.2 Programming Technique

The single transputer programs have been compiled and executed on the root T800 transputer of the B008 motherboard. All single transputer programs have been implemented as Parallel C programs which use none of the parallel features of the language. In particular, no processes are allocated or run, no channels are used and no message passing is performed. With only minor modifications, these programs could be compiled and run on a standard computer architecture with a standard C compiler such as a Sun 4 running ANSI C under UNIX. Each program performs its computation on the image and outputs the result (a convolved binary image in the case of convolution, sixteen moments in the case of regular moments) to files on the host. The time taken for computation alone is then printed on the host monitor.

## 4.3 Convolution

The convolution algorithm presented in Section 3.5.1 has been implemented on a single transputer using Parallel C. Both the image and mask are acquired from files on the host. The image pixels are stored as single byte Parallel C char data types. The mask elements are stored as float data types. In Parallel C these are implemented as 32 bit IEEE floating point numbers. To maintain full flexibility for convolving an arbitrary sized image and with an arbitrary sized mask, the mask and image are stored in dynamically allocated buffers rather than in static Parallel C arrays. Offsets into these buffers are maintained in order to reduce the time needed to reference elements.

Due to the large number of multiplications and additions needed, the convolution algorithm runs relatively slowly. The program has been run on images with dimensions equal to powers of two from 64 to 1024 for four different sized real masks. Table

4.1 shows all the execution times in seconds. N represents the image size, M the mask size.

| M $N$ | 64     | 128   | 256   | 512   | 1024  |

|-------|--------|-------|-------|-------|-------|

| 3     | 0.3239 | 1.293 | 5.166 | 20.65 | 82.61 |

| 5     | 0.7338 | 2.934 | 11.73 | 46.93 | 187.7 |

| 7     | 1.33   | 5.325 | 21.31 | 85.24 | 341   |

| 13    | 4.237  | 16.99 | 68.02 | 272.2 | 1098  |

Table 4.1: Single Transputer Convolution Timing Results in Seconds

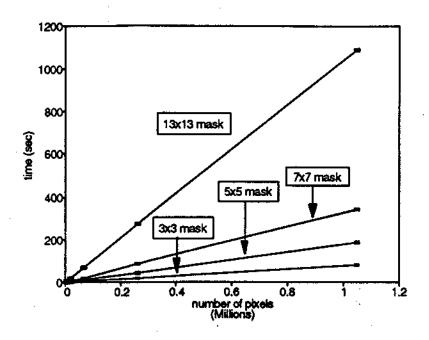

Figure 4.1 gives a plot of the execution time against the number of image pixels for the four different mask sizes. The execution time increases linearly with the number of image pixels (quadratically with image size N). A graph of the convolution execution times as the mask size increases for the five different sized images is given in Figure 4.2. The reader can verify that the times increase slightly less than linearly with the number of mask elements by examining Table 4.1. This is due to the fact that the multiplications and additions involved in convolution must be performed not only on the image pixels but also on the border of zeros added around the image. The arithmetic operations on zero element values seem to be slightly faster than arithmetic with any other value in Parallel C on the T800 transputer. Furthermore, the number of additions required to maintain the buffer offsets increases less than linearly with the number of mask elements. We have modified the convolution program to accept integer masks. Not surprisingly, the execution times are faster than those achieved with floating point masks, since integer arithmetic operations are faster than floating point ones.

# 4.4 Regular Moments

The six pure and two of the hybrid moment extraction algorithms described in Section 3.6.2 have also been implemented on a single transputer. As is the case with the convolution implementation, the images are acquired from host files and stored

Figure 4.1: Convolution Timing Results for Various Mask Sizes

Figure 4.2: Convolution Timing Results for Various Image Sizes

in buffers of Parallel C char types. Offsets into these buffers are again maintained during execution of the programs. The first sixteen moments are found by all the implementations. They are calculated as Parallel C double types. These are implemented as 64 bit IEEE double precision floating point numbers. The moments are printed to a host file at the end of each implementation. Each program was run on the same five image sizes as the convolution program. Table 4.2 shows the timing results in seconds. N is the image size. ISM indicates there was insufficient memory to run the program on the image size in question.

| algorithm N      | 64      | 128    | 256    | 512   | 1024  |

|------------------|---------|--------|--------|-------|-------|

| straightforward  | 21.27   | 85.5   | 342.8  | 1373  | 5495  |

| coefficient      | 1.069   | 4.26   | 17.01  | ISM   | ISM   |

| column products  | 0.7935  | 3.158  | 12.6   | ISM   | ISM   |

| recursive        | 0.05888 | 0.2249 | 0.8803 | 3.484 | 13.86 |

| add and multiply | 0.1648  | 0.6634 | 2.484  | 9.839 | 39.17 |

| partial sum      | 0.4648  | 2.08   | 9.322  | 41.57 | 184   |

| recurse/multiply | 0.06522 | 2.375  | 0.9055 | 3.534 | 13.96 |

| recurse/partial  | 0.08723 | 0.2921 | 1.036  | 3.839 | 14.66 |

Table 4.2: Single Transputer Regular Moment Timing Results in Seconds

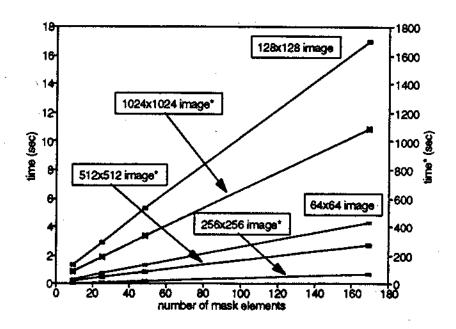

Figure 4.3 contains a graph of the execution times of the straightforward algorithm plotted against the number of image pixels. The execution time increases approximately linearly with the number of image pixels. Due to the large number of additions, multiplications and exponent calculations required, this is by far the slowest of the single transputer implementations.

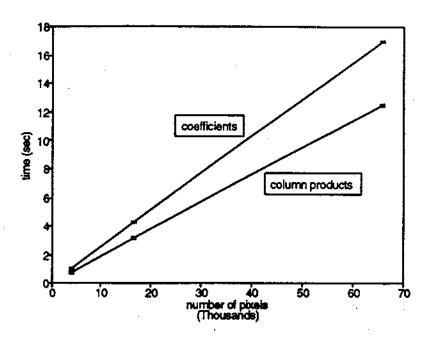

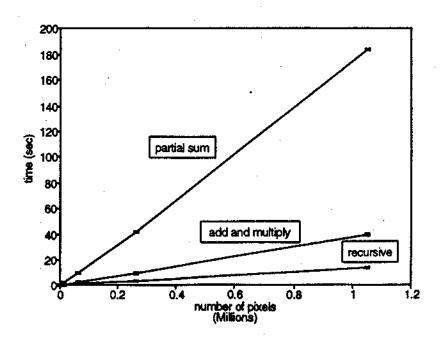

Similar graphs of execution times versus number of image pixels for the coefficient storage and column product programs are given in Figure 4.4. Again, linear increases in the execution times with the number of pixels are shown. There was insufficient memory for these two programs to be run on images greater than  $256 \times 256$ . The timing results for the two dimensional partial sum, add and multiply and recursive algorithm implementations are plotted in Figure 4.5. The times for the recursive and the add and multiply implementations increase slightly less than linearly with the

Figure 4.3: Straightforward Algorithm Timing Results

number of image pixels. However, the execution time of the partial sum implementation increases more than linearly with the number of pixels. The reader can confirm these observations by referring to Table 4.2. These three programs are in fact the fastest single transputer moment implementations.

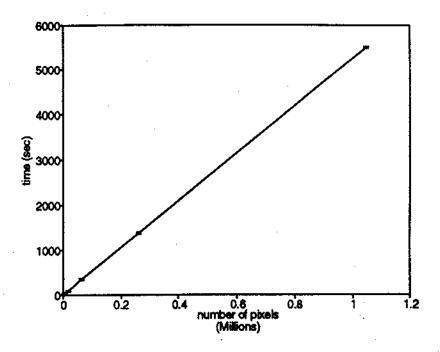

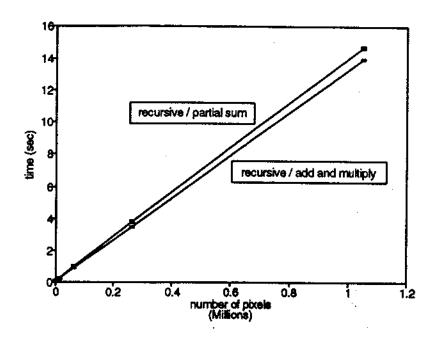

In order to allow speedup and efficiency analyses to be performed in Chapter 5 on two of the multi-transputer programs, the recursive/partial sum and recursive/add and multiply hybrid algorithms have also been implemented. Figure 4.6 contains graphs of the execution times of these two single transputer hybrid programs. The execution times here increase slightly less than linearly. This can confirmed by referring to Table 4.2.

We believe that the timing results of the four hybrid algorithms not implemented would fall between those of the two pure programs involved. A final observation is that when the data type of the moments is changed from double to single precision

Figure 4.4: Coefficient and Column Product Algorithm Timing Results

Figure 4.5: Recursive, Partial Sum and Add and Multiply Algorithm Timing Results

Figure 4.6: Hybrid Algorithm Timing Results

in the recursive program, a significant decrease in execution times results. We expect that similar reductions would occur if single precision moments were calculated in the other programs. Some loss of accuracy in the moments extracted results when this is done, however.

# 4.5 Remarks

All the single transputer programs were compiled using icconf and a configuration source file. Alternatively, they can be compiled without a configuration source file using the single transputer option of icollect. (See Section 2.6.3 for a description of the transputer compilation procedure.) The latter method produces significantly faster running programs. We believe that is this due to the fact that less general code is produced if no parallel programming features are needed. Our method of compilation

allows fairly accurate multi-transputer models to be presented in Chapter 6 since the multi-transputer programs need to be compiled in the most general parallel way. The single transputer implementations themselves are quite extensive. However, we believe the time spent programming them was worthwhile since they provide a good foundation for the multi-transputer programs presented next.

# Chapter 5

# Multi-Transputer Implementations

## 5.1 Introduction

Four multi-transputer implementations of both convolution and regular moments have been realized. Our goals in doing so are loftier than they are in the single transputer case. Certainly we wish to create fast programs for performing convolution and for calculating regular moments on the B008 using Parallel C. In the process, however, we also wish to determine and investigate the issues related to image processing on transputers in general. In particular, we want to discover useful principles and to create strategies for implementing more general image processing applications efficiently on multiple transputers.

This chapter begins with a description of the programming technique we have used in the multi-transputer case. Next, descriptions of the issues relevant to image processing on transputers and our strategies for dealing with them are presented. A section describing the multi-transputer implementations for convolution is followed by a similar section that gives the details of the regular moment multi-transputer implementations. Analysis of the implementations is given next. As usual, the chapter

# 5.2 Programming Technique

The entire B008 motherboard is used in the multi-transputer implementations. (See Section 2.5.7 for a full description of the B008 and its operation.) Our method of programming here is quite different from that used in the single transputer implementations. In the single transputer case, a Parallel C program running on the root transputer is not only responsible for controlling input and output to the host but also for all computations needed to perform the image processing tasks. The other transputers are not used. However, in our multi-transputer implementations, all nine transputers may be used. Parallel C is again used. In this case, however, one separate asynchronous linked unit process executes on each transputer used. The root transputer is still responsible for data transfers to and from the host. All of the necessary computations are executed on the other eight transputers.

Each transputer has been programmed using the optimal transputer programming method discussed in Section 2.5.9. All local channels and processes are declared as global variables in the source file for each transputer. The main() function of each source file is used to allocate channels, allocate and run processes and to time the implementation. Processes are run asynchronously in parallel using the ProcRun() function. A channel is created for communication between each pair of processes that communicate in each direction they communicate. Aside from channels and processes, global data structures have been kept to a minimum. In this way, the problems of mutual exclusion are avoided that usually occur when more than one concurrent process accesses the same data. As in Hoare's model, each process keeps its own copy of data. This data can be sent to another process using message passing on a local channel. Configuration source files (see Section 2.6.2) are used to map the linked units to the appropriate transputer on the B008 for execution.

# 5.3 General Issues and Strategies

When we began this part of the research, we were confronted with many interesting and challenging questions. Among these were: "What parallelization techniques should be used?", "How should data be passed?", "What moment algorithm should be chosen?" and "What topologies are best for image processing?". For each question, a number of solutions are possible. One approach that we considered was simply to select one possible solution to each problem and to design and program an implementation. We could find the best implementations by simply repeating that process for all reasonable possibilities.